# A31G324, A31G323 User's Manual

# 32-bit Cortex-M0+ based General Purpose Microcontroller

Version 1.07

## Introduction

This user's manual contains complete information for application developers who use A31G324 or A31G323 for their specific needs.

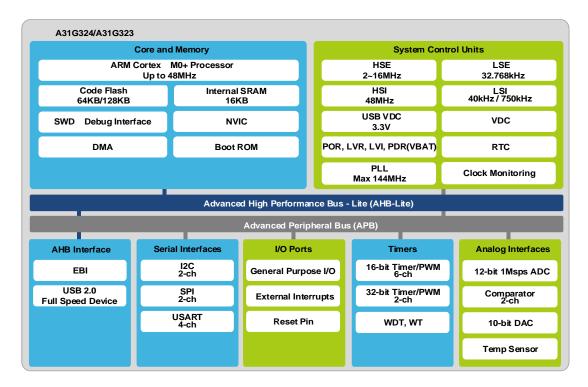

A31G32x devices are 32-bit general purpose microcontrollers for various USB appliances. To meet the requirements for the complexity and high performance in consumer and portable electronics, A31G32x incorporate ARM's high-speed 32-bit Cortex-M0+ Cores, USB full speed interface, high speed ADC, various power mode for power consumption reduction, plentiful analog functions, and high resolution PWM for precision control and data processing.

Building on the very successful Cortex-M0+ processor, the ARM® Cortex®-M0+ retains full instruction set and tool compatibility, while further reducing energy consumption and increasing performance.

## **Reference document**

• Document 'DDI 0484C' is provided by ARM and contains information of Cortex-M0+.

## Contents

| Intro | ntroduction1 |                |                                                                        |     |  |

|-------|--------------|----------------|------------------------------------------------------------------------|-----|--|

| Refe  | rence o      | documei        | nt                                                                     | 1   |  |

| 1     | Descr        | iption         |                                                                        | .19 |  |

|       | 1.1          | Device         | overview                                                               | .19 |  |

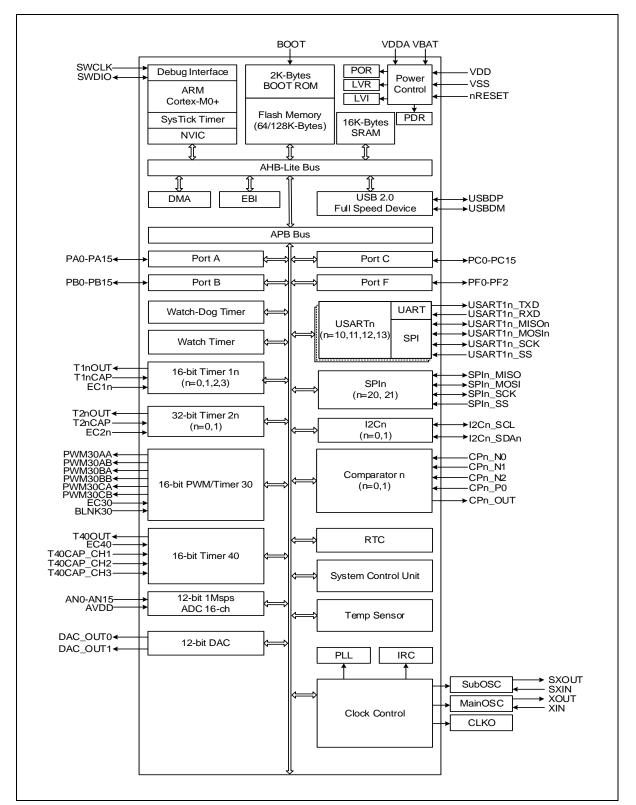

|       | 1.2          |                | liagram                                                                |     |  |

| 2     | Pinout       | ts and p       | in descriptions                                                        | .23 |  |

|       | 2.1          |                | 5                                                                      |     |  |

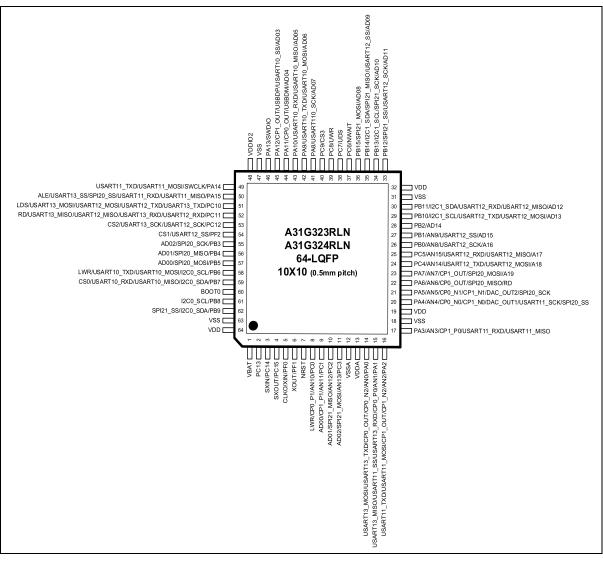

|       |              | 2.1.1          | A31G323RLN, A31G324RLN (64 LQFP)                                       | .23 |  |

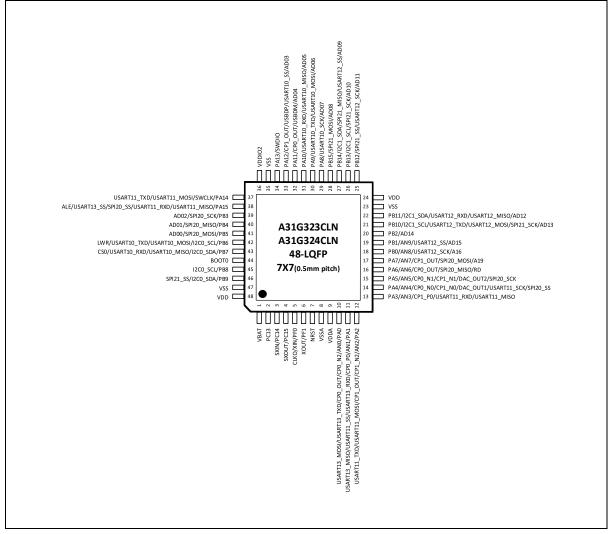

|       |              | 2.1.2          | A31G323CLN, A31G324CLN (48 LQFP)                                       |     |  |

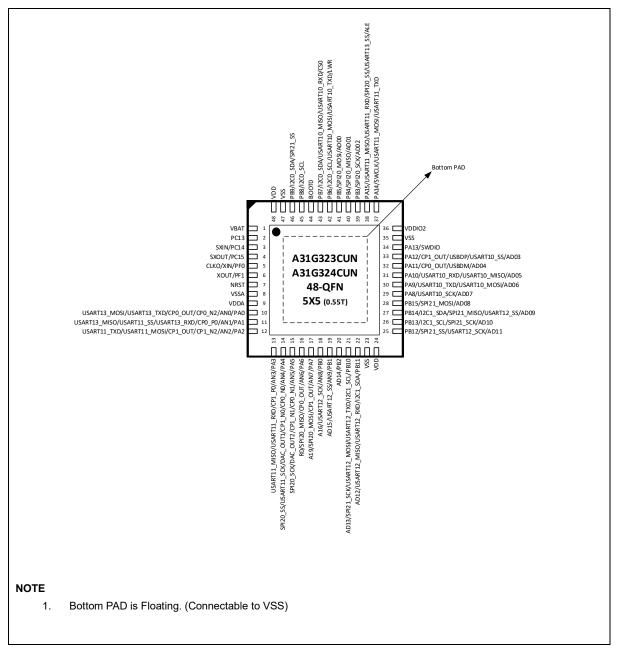

|       |              | 2.1.3          | A31G323CUN, A31G324CUN (48 QFN)                                        |     |  |

|       | 2.2          |                | scription                                                              |     |  |

| 3     | Syster       |                | nemory overview                                                        |     |  |

|       | 3.1          | System         | n architecture                                                         |     |  |

|       |              | 3.1.1          | Cortex-M0+ Core                                                        |     |  |

|       |              | 3.1.2          | Interrupt controller                                                   |     |  |

|       | 3.2          |                | y organization                                                         |     |  |

|       |              | 3.2.1          | Register boundary address                                              |     |  |

|       |              | 3.2.2          | Memory map                                                             |     |  |

|       |              | 3.2.3          | Embedded SRAM                                                          |     |  |

|       |              | 3.2.4          | Flash memory overview                                                  |     |  |

|       |              | 3.2.5          | Boot mode                                                              |     |  |

| 4     | •            |                | bl unit                                                                |     |  |

|       | 4.1          |                | ock diagram                                                            |     |  |

|       | 4.2          |                | system                                                                 |     |  |

|       |              | 4.2.1          | HCLK clock domain                                                      |     |  |

|       |              | 4.2.2          | PCLK clock domain                                                      |     |  |

|       |              | 4.2.3          | Clock configuration procedure                                          |     |  |

|       | 4.3          |                | domain                                                                 |     |  |

|       | 4.4          |                |                                                                        |     |  |

|       |              | 4.4.1          | Cold reset                                                             |     |  |

|       |              | 4.4.2          | Warm reset                                                             |     |  |

|       |              | 4.4.3          | LVR reset                                                              |     |  |

|       |              | 4.4.4          | Reset tree                                                             |     |  |

|       | 4.5          | •              | ion mode                                                               |     |  |

|       |              | 4.5.1          | RUN mode                                                               |     |  |

|       |              | 4.5.2          | SLEEP mode                                                             |     |  |

|       |              | 4.5.3          | Power-down mode                                                        |     |  |

|       |              | 4.5.4          | STOP mode                                                              |     |  |

|       |              | 4.5.5          | STANDBY mode                                                           |     |  |

|       | 16           | 4.5.6          | BACKUP POWER mode                                                      |     |  |

|       | 4.6          | 4.6.1          | ers                                                                    |     |  |

|       |              | 4.6.1          | SCUCC_VENDORID: vendor ID register                                     |     |  |

|       |              | 4.6.2<br>4.6.3 | SCUCC_CHIPID: chip ID register                                         |     |  |

|       |              | 4.6.3<br>4.6.4 | SCUCC_REVNR: revision number register<br>SCU_SMR: system mode register |     |  |

|       |              | 4.6.4<br>4.6.5 | SCU_SMR. system mode register                                          |     |  |

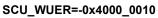

|       |              | 4.6.5<br>4.6.6 | SCU_WUER: wakeup source enable register                                |     |  |

|       |              | 4.6.6<br>4.6.7 |                                                                        |     |  |

|       |              | 4.0.7          | SCU_WUSR: wakeup source status register                                | 09  |  |

|       | 4.6.8  | SCU_RSER: reset source enable register                     | 71  |

|-------|--------|------------------------------------------------------------|-----|

|       | 4.6.9  | SCU_RSSR: reset source status register                     |     |

|       |        | SCU_PRER1: peripheral reset enable register 1              |     |

|       |        | SCU_PRER2: peripheral reset enable register 2              |     |

|       |        | SCU_PER1: peripheral enable register1                      |     |

|       |        | SCU_PER2: peripheral enable register 2                     |     |

|       | 4.6.14 | SCU_PCER1: peripheral clock enable register 1              | 77  |

|       |        | SCU_PCER2: peripheral clock register 2                     |     |

|       | 4.6.16 | SCU_PPCLKSR: peripheral clock selection register           | 79  |

|       |        | SCU_CSCR: clock source control register                    |     |

|       | 4.6.18 | SCU_SCCR: system clock control register                    | 81  |

|       | 4.6.19 | SCU_CMR: clock monitoring register                         | 81  |

|       | 4.6.20 | SCU_NMIR: NMI control register                             | 83  |

|       | 4.6.21 | SCU_COR: clock output register                             | 84  |

|       | 4.6.22 | SCU_PLLCON: PLL control register                           | 85  |

|       | 4.6.23 | SCU_VDCCON: VDC control register                           | 87  |

|       | 4.6.24 | SCU_PDRCON: PDR control register                           | 88  |

|       | 4.6.25 | SCU_LSICON: Low speed internal OSC control register        | 89  |

|       | 4.6.26 | SCU_EOSCR: External oscillator control register            | 89  |

|       | 4.6.27 | SCU_EMODR: External mode status register                   | 90  |

|       | 4.6.28 | SCU_RSTDBCR: pin reset debounce control register           | 91  |

|       | 4.6.29 | SCU_MCCR1: Miscellaneous clock control register 1          | 92  |

|       | 4.6.30 | SCU_MCCR2: Miscellaneous clock control register 2          | 93  |

|       |        | SCU_MCCR3: Miscellaneous clock control register 3          |     |

|       |        | SCU_MCCR4: Miscellaneous clock control register 4          |     |

|       |        | SCU_MCCR5: Miscellaneous clock control register 5          |     |

|       |        | SCU_MCCR6: Miscellaneous clock control register 6          |     |

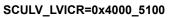

|       |        | SCULV_LVICR: Low voltage indicator control register        |     |

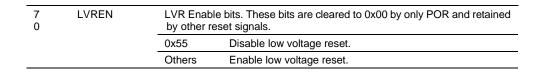

|       |        | SCULV_LVRCR: Low voltage reset control register            |     |

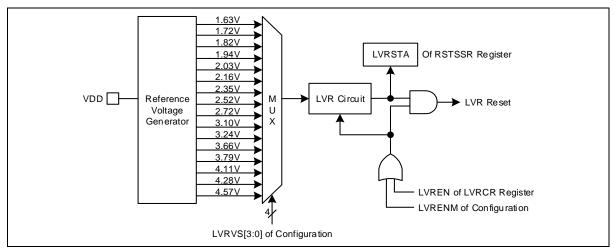

|       |        | SCULV_LVRCNFIG: Configuration for low voltage reset        |     |

| PCU a |        | 0                                                          |     |

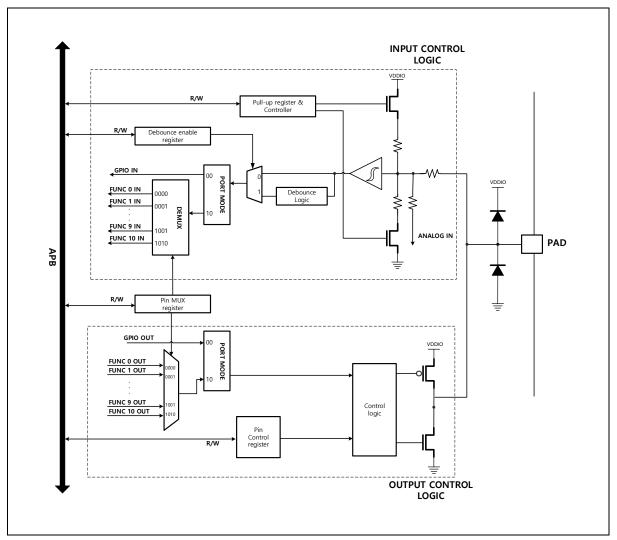

| 5.1   |        | nd GPIO Block diagram                                      |     |

| 5.2   |        | Itiplexing                                                 |     |

| 5.3   |        | ۲۰۰۶                                                       |     |

|       | 5.3.1  | Pn_MOD: PORT n mode register                               |     |

|       | 5.3.2  | Pn_TYP: Port n output type selection register              |     |

|       | 5.3.3  | Pn_AFSR1: Port n alternative function selection register 1 |     |

|       | 5.3.4  | Pn_AFSR2: Port n alternative function selection register 2 |     |

|       | 5.3.5  | Pn_PUPD: Port n pull-up/down resistor selection register   |     |

|       | 5.3.6  | Pn_INDR: Port n input data register                        |     |

|       | 5.3.7  | Pn_OUTDR: Port n output data register                      |     |

|       | 5.3.8  | Pn_BSR: Port n output bit set register                     |     |

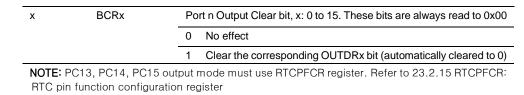

|       | 5.3.9  | Pn_BCR: Port n output bit clear register                   |     |

|       | 5.3.10 | Pn_OUTDMSK: Port n output data mask register               |     |

|       |        | Pn_DBCR: Port n debounce control register                  |     |

|       |        | Pn_IER: Port n interrupt enable register                   |     |

|       |        | Pn_ISR: Port n interrupt status register                   |     |

|       |        | Pn_ICR: Port n interrupt control register                  |     |

|       |        | PCU_USBCON: USB control register                           |     |

|       |        |                                                            |     |

|       | 5.5.10 | PCU_PORTEN: Port access enable                             | 115 |

5

|    | 5.4    | Functio  | nal description                                     | . 116 |

|----|--------|----------|-----------------------------------------------------|-------|

| 6  | Flash  | memory   | <i>i</i> controller                                 | . 118 |

|    | 6.1    | Registe  | ers                                                 | . 120 |

|    |        | 6.1.1    | FMC_MR: Flash memory mode register                  | . 121 |

|    |        | 6.1.2    | FMC_CR: Flash memory control register               | . 121 |

|    |        | 6.1.3    | FMC_AR: Flash memory address register               | . 122 |

|    |        | 6.1.4    | FMC_DR: Flash data input register                   | . 122 |

|    |        | 6.1.5    | FMC_BUSY: Flash write busy status register          | . 123 |

|    |        | 6.1.6    | FMC_CRC: Flash CRC check register                   | . 123 |

|    |        | 6.1.7    | FMC_CFG: Flash memory configuration register        | . 124 |

|    |        | 6.1.8    | FMC_WPROT: Write protection register                | . 124 |

|    |        | 6.1.9    | FMC_LOCK: Flash lock register                       | . 125 |

|    | 6.2    | Functio  | nal description                                     | . 126 |

|    |        | 6.2.1    | Flash erase and program examples                    | . 126 |

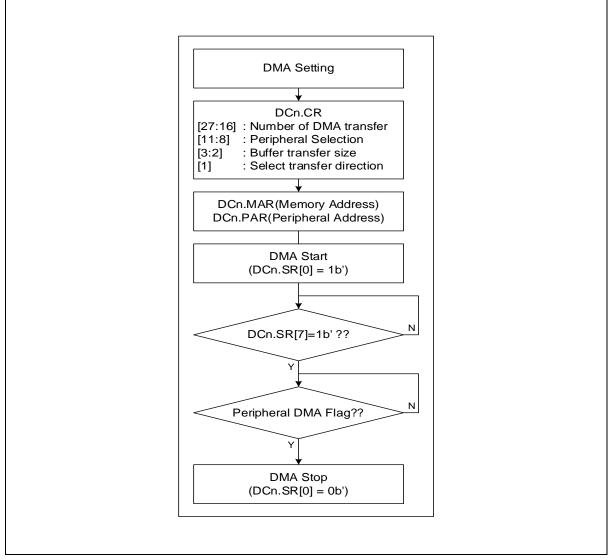

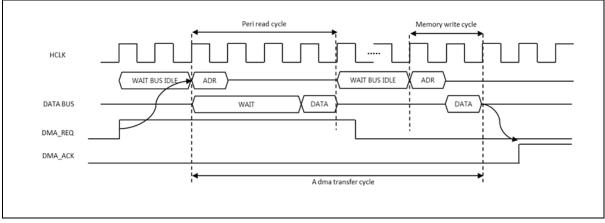

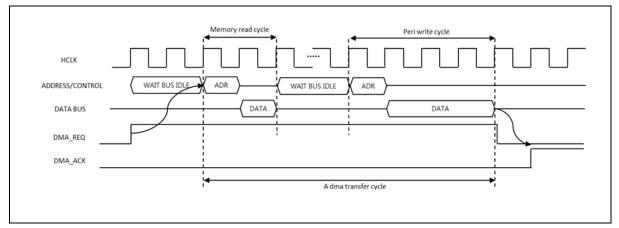

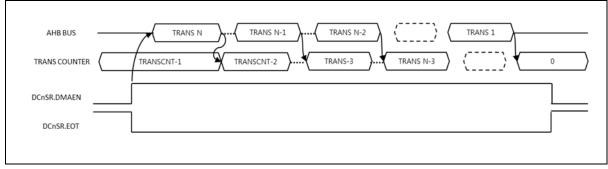

| 7  | Direct | Memory   | y Access Controller (DMAC)                          | . 129 |

|    | 7.1    | Block d  | liagram                                             | . 129 |

|    | 7.2    | Registe  | -<br>Prs                                            | . 130 |

|    |        | 7.2.1    | DCn.CR: DMA controller configuration register       | . 130 |

|    |        | 7.2.2    | DCn.SR: DMA controller status register              | . 132 |

|    |        | 7.2.3    | DCn.PAR: DMA controller peripheral address register | . 132 |

|    |        | 7.2.4    | DCn.MAR: DMA controller memory address register     | . 133 |

|    | 7.3    | Functio  | nal description                                     | . 134 |

|    |        | 7.3.1    | DMA operation                                       | . 135 |

| 8  | Static | memory   | / controller (EBI)                                  | . 138 |

|    | 8.1    | Block d  | liagram                                             | . 139 |

|    | 8.2    | Registe  | -<br>Prs                                            | . 139 |

|    |        | 8.2.1    | SMIBCRn: Memory area configuration register n       | . 140 |

|    | 8.3    | Functio  | nal description                                     | . 141 |

|    |        | 8.3.1    | Chip select signal                                  | . 141 |

|    |        | 8.3.2    | Byte lane control and control signal                | . 141 |

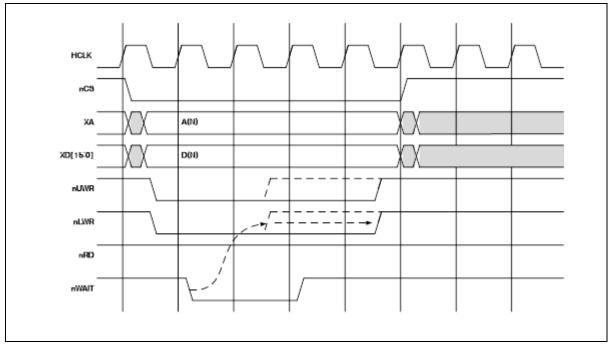

|    |        | 8.3.3    | Bus control signal in read operation                | . 144 |

|    |        | 8.3.4    | Bus control signal in write operation               | . 147 |

|    |        | 8.3.5    | Timing change of control signals                    | . 150 |

|    |        | 8.3.6    | Wait control while accessing memory                 | . 151 |

| 9  | Watch  | ndog tim | er (WDT)                                            | . 152 |

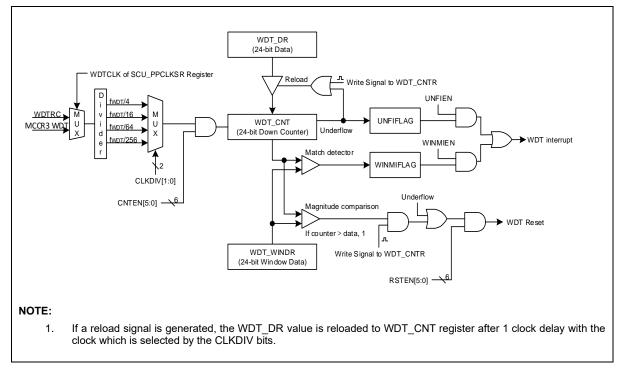

|    | 9.1    | WDT b    | lock diagram                                        | . 152 |

|    | 9.2    | Registe  | ers                                                 | . 153 |

|    |        | 9.2.1    | WDT_CR: Watchdog timer control register             | . 154 |

|    |        | 9.2.2    | WDT_SR: Watchdog timer status register              | . 155 |

|    |        | 9.2.3    | WDT_DR: Watchdog timer data register                | . 155 |

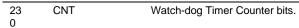

|    |        | 9.2.4    | WDT_CNT: Watchdog timer counter register            | . 156 |

|    |        | 9.2.5    | WDT_WINDR: Watchdog timer window data register      | . 156 |

|    |        | 9.2.6    | WDT_CNTR: Watchdog timer counter reload register    | . 157 |

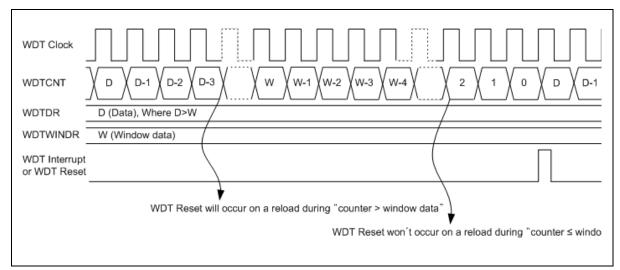

|    | 9.3    | Functio  | nal description                                     | . 157 |

|    |        | 9.3.1    | Timing diagram                                      | . 158 |

|    |        | 9.3.2    | Prescale table                                      | . 158 |

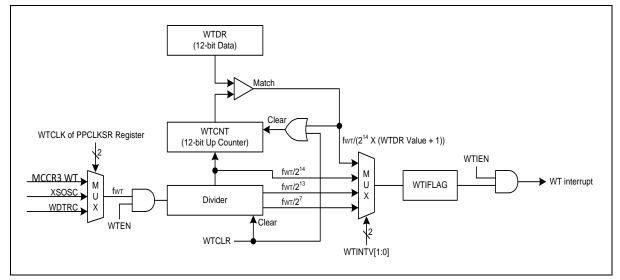

| 10 | Watch  | n timer  |                                                     | . 159 |

|    | 10.1   | WT blo   | ck diagram                                          | . 159 |

|    | 10.2   | Registe  | ers                                                 | . 160 |

|    |        | 10.2.1   | WT_CR: Watch timer control register                 | . 161 |

|    |        |          |                                                     |       |

|    |        | 10.2.2   | WT_DR: Watch timer data register                                      | 162 |

|----|--------|----------|-----------------------------------------------------------------------|-----|

|    |        | 10.2.3   | WT_CNT: Watch timer counter register                                  | 162 |

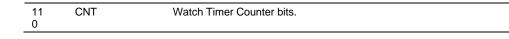

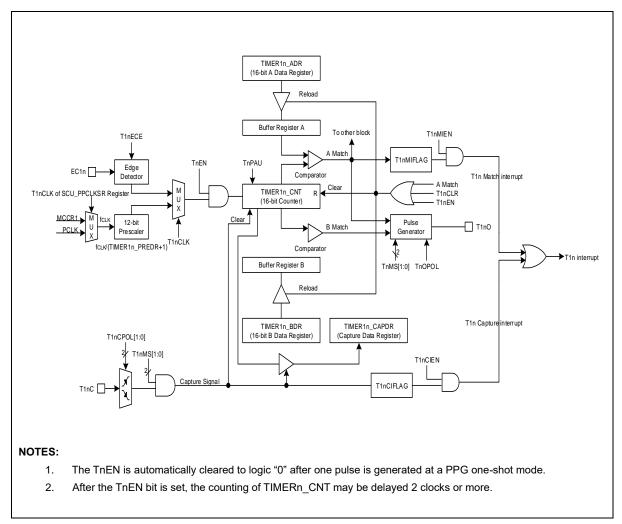

| 11 | 16-bit | timer    |                                                                       | 163 |

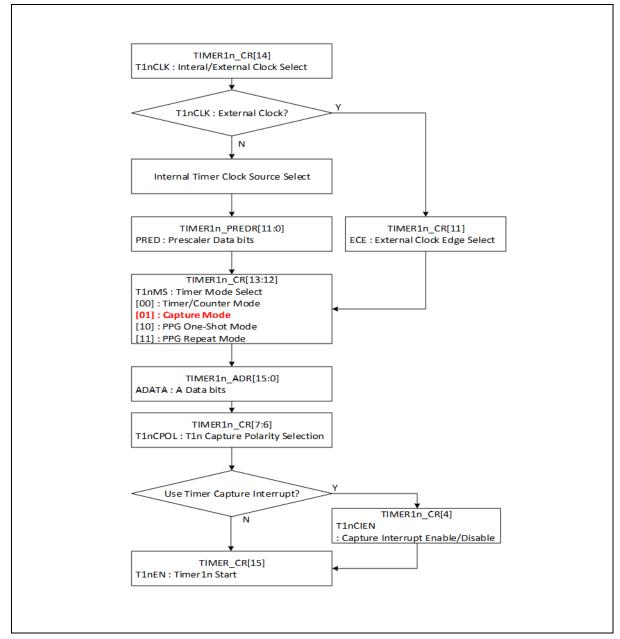

|    | 11.1   | 16-bit t | imer block diagram                                                    | 164 |

|    | 11.2   | Registe  | ers                                                                   | 164 |

|    |        | 11.2.1   | TIMER1n_CR: Timer/counter 1n control register                         | 165 |

|    |        | 11.2.2   | TIMER1n_ADR: Timer/counter 1n A data register                         | 167 |

|    |        | 11.2.3   | TIMER1n_BDR: Timer/counter n B data register                          | 167 |

|    |        | 11.2.4   | TIMER1n_CAPDR: Timer/counter 1n capture data register                 | 168 |

|    |        | 11.2.5   | TIMER1n_PREDR: Timer/counter 1n prescaler data register               | 168 |

|    |        | 11.2.6   | TIMER1n_CNT: Timer/counter n counter register                         | 168 |

|    | 11.3   |          | onal description                                                      |     |

|    |        | 11.3.1   | Timer counter 10/11/12/13                                             | 169 |

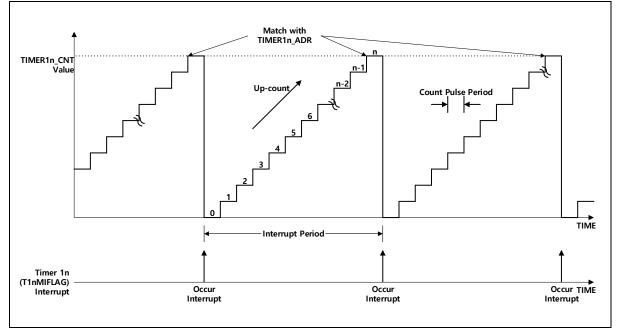

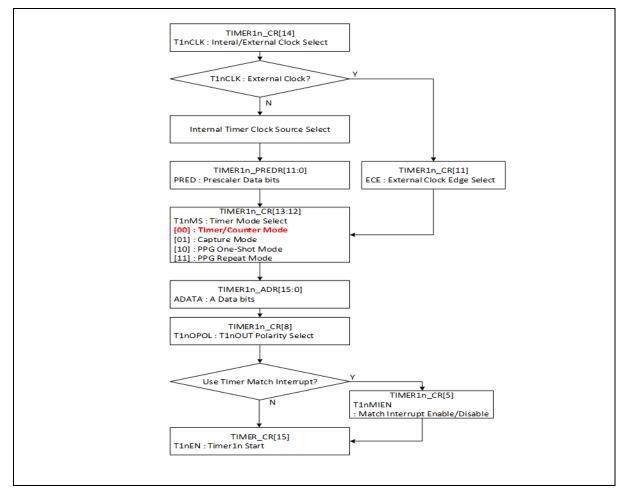

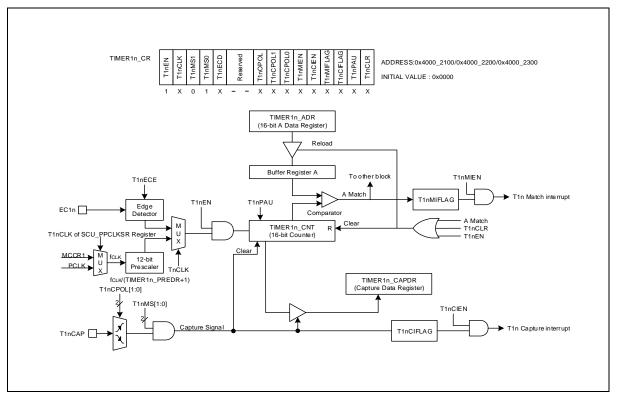

|    |        | 11.3.2   | 16-bit timer/counter mode                                             | 170 |

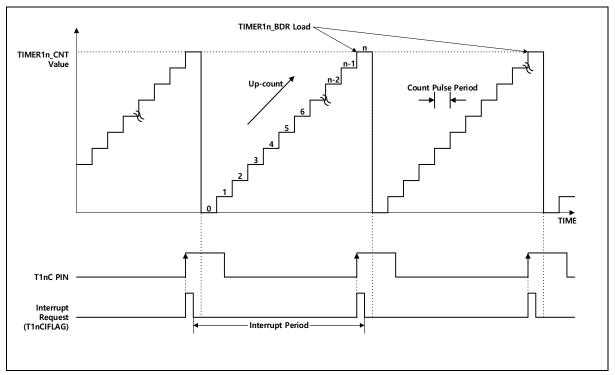

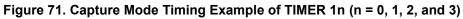

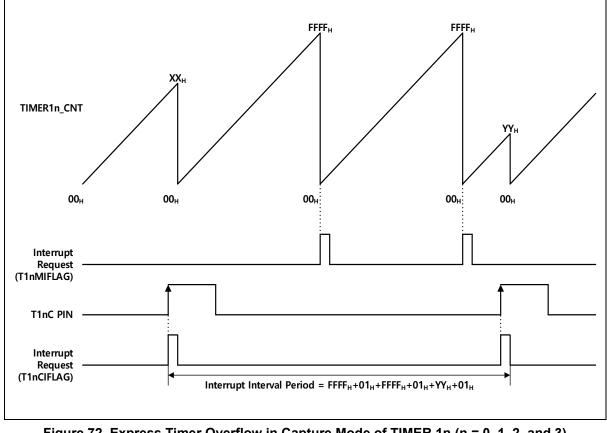

|    |        | 11.3.3   | 16-bit capture mode                                                   | 172 |

|    |        |          | 16-bit PPG mode                                                       |     |

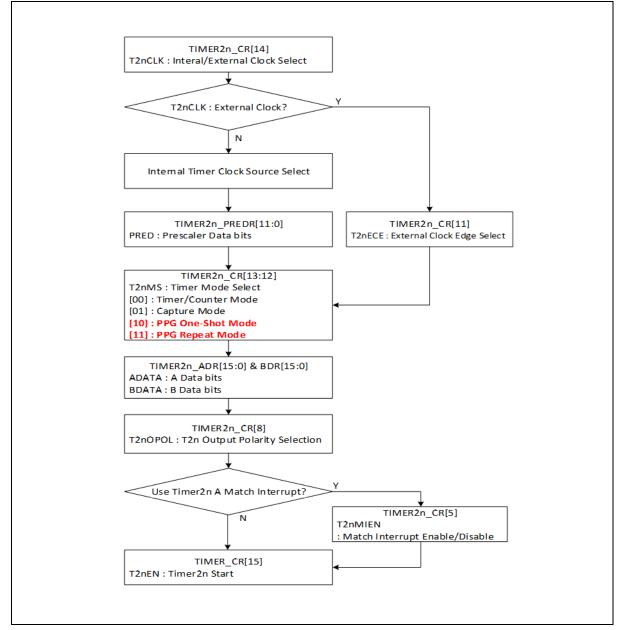

| 12 | 32-bit |          |                                                                       |     |

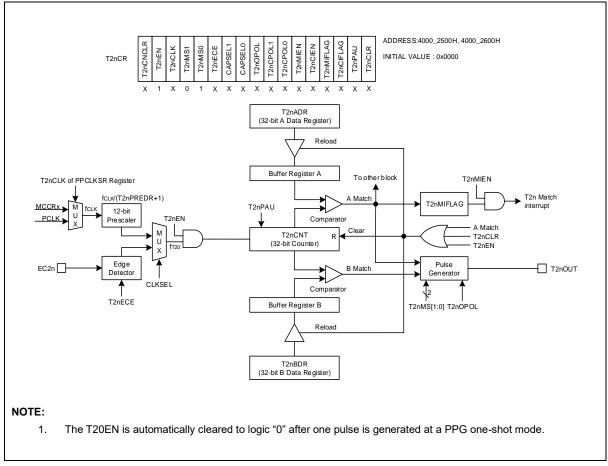

|    | 12.1   |          | imer block diagram                                                    |     |

|    | 12.2   |          | ərs                                                                   |     |

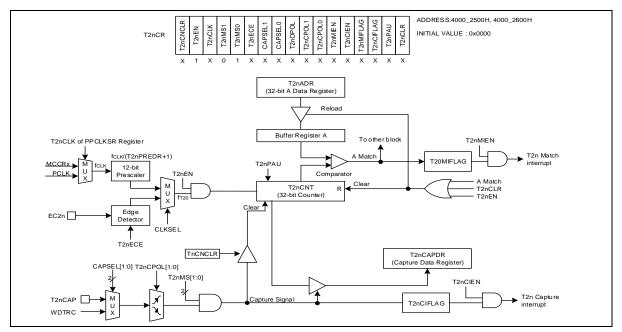

|    |        | 0        | TIMER2n_CR: Timer/counter 2n control register                         |     |

|    |        |          | TIMER2n_ADR: Timer/counter 2n A data register                         |     |

|    |        |          | TIMER2n_BDR: Timer/counter 2n B data register                         |     |

|    |        |          | TIMER2n_CAPDR: Timer/counter 2n capture data register                 |     |

|    |        |          | TIMER2n_PREDR: Timer/counter 2n prescaler data register               |     |

|    |        |          | TIMER2n_CNT: Timer/counter 2n counter register                        |     |

|    | 12.3   |          | onal description                                                      |     |

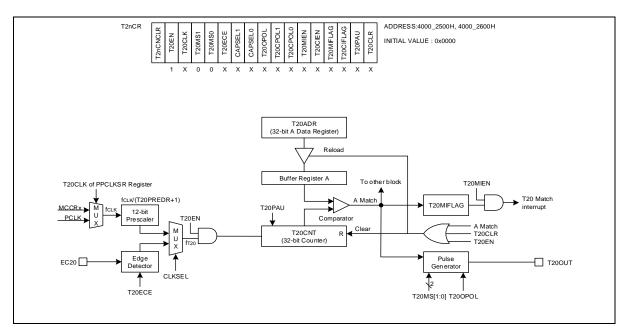

|    | 12.0   |          | Timer counter 2n                                                      |     |

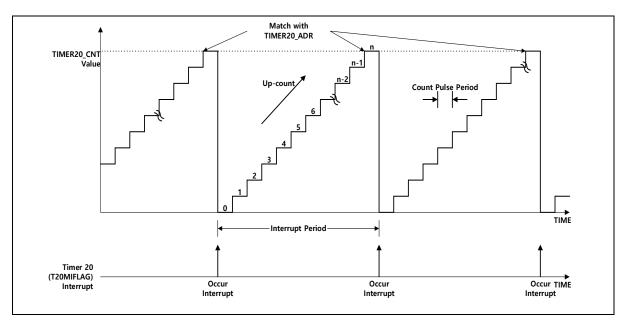

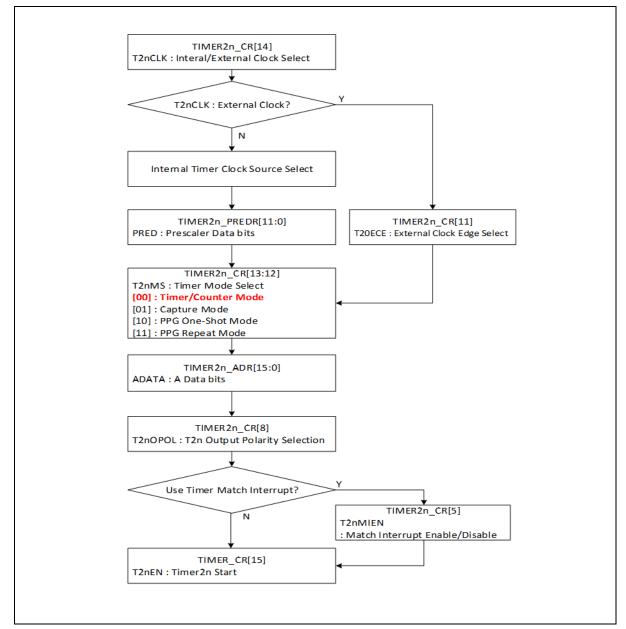

|    |        |          | 32-bit timer/counter mode                                             |     |

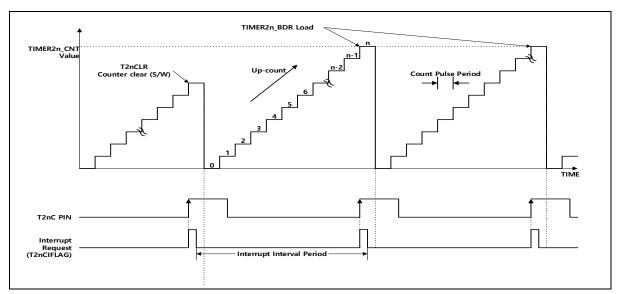

|    |        |          | 32-bit capture mode                                                   |     |

|    |        |          | 32-bit PPG mode                                                       |     |

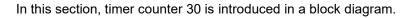

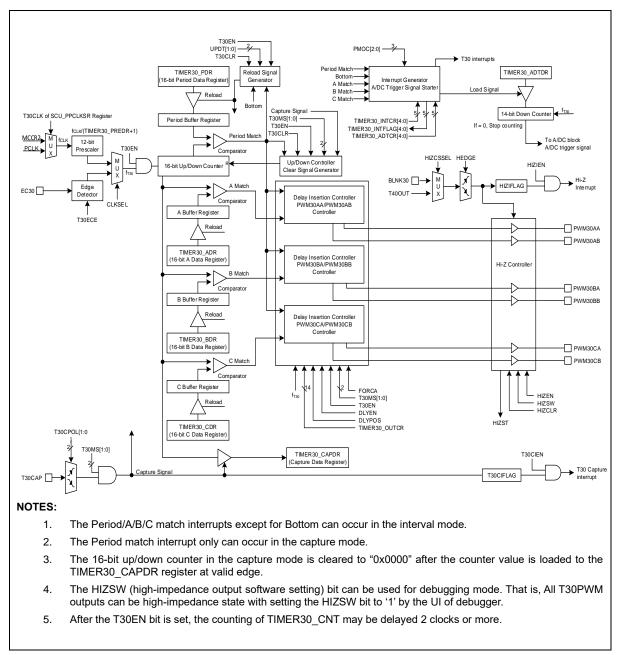

| 13 | Timor  |          | 32-bit FFG mode                                                       |     |

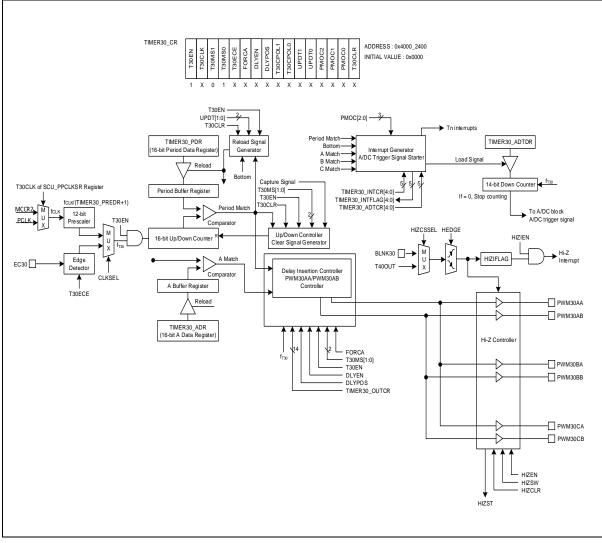

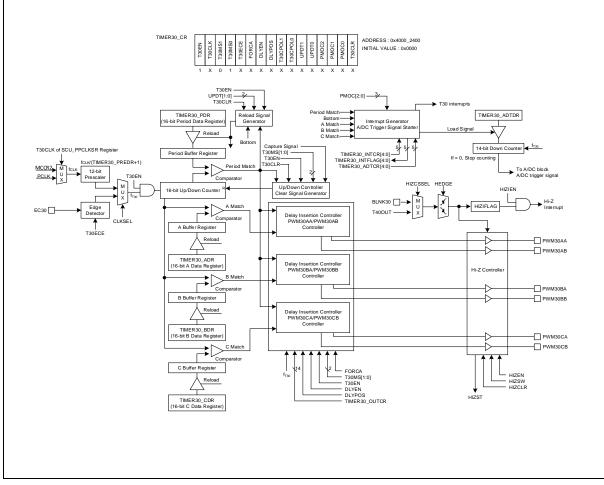

| 15 | 13.1   |          | counter 30 block diagram                                              |     |

|    | 13.1   |          | ers                                                                   |     |

|    | 13.2   |          | TIMER30_CR: Timer/counter 30 control register                         |     |

|    |        |          |                                                                       |     |

|    |        |          | TIMER30_PDR: Timer/counter 30 period data register                    |     |

|    |        |          | TIMER30_ADR: Timer/counter 30 A data register                         |     |

|    |        |          | TIMER30_BDR: Timer/counter 30 B data register                         |     |

|    |        |          | TIMER30_CDR: Timer/counter 30 C data register                         |     |

|    |        |          | TIMER30_CAPDR: Timer/counter 30 capture data register                 |     |

|    |        |          | TIMER30_PREDR: Timer/counter 30 prescaler data register               |     |

|    |        |          | TIMER30_CNT: Timer/counter 30 counter register                        |     |

|    |        |          | TIMER30_OUTCR: Timer/counter 30 output control register               |     |

|    |        |          | OTIMER30_DLY: Timer/counter 30 PWM output delay data register         |     |

|    |        |          | I TIMER30_INTCR: Timer/counter 30 interrupt control register          |     |

|    |        |          | 2 TIMER30_INTFLAG: Timer/counter 30 interrupt flag register           |     |

|    |        |          | 3TIMER30_HIZCR: Timer/counter 30 high-impedance control register      |     |

|    |        |          | Image: Timer Timer Counter 30 A/DC trigger control register           |     |

|    |        |          | 5TIMER30_ADTDR: Timer/counter 30 A/DC trigger generator data register |     |

|    | 13.3   |          | onal description                                                      |     |

|    |        | 13.3.1   | Timer counter 30                                                      | 208 |

|    |        |          | Timer 30 capture mode                                      |     |

|----|--------|----------|------------------------------------------------------------|-----|

|    |        | 13.3.3   | Timer 30 interval mode                                     | 211 |

| 14 | Timer  | counter  | 40                                                         | 223 |

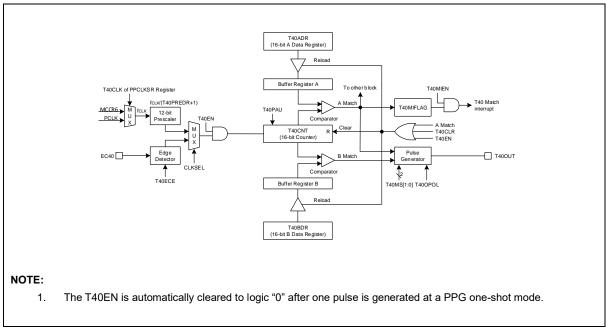

|    | 14.1   | Timer c  | counter 40 block diagram                                   | 224 |

|    | 14.2   | Registe  | ers                                                        | 225 |

|    |        | 14.2.1   | TIMER40_CR: Timer/counter 40 control register              | 226 |

|    |        | 14.2.2   | TIMER40_ADR: Timer/counter 40 A data register              | 227 |

|    |        | 14.2.3   | TIMER40 BDR: Timer/counter 40 B data register              | 228 |

|    |        | 14.2.4   | TIMER40 CAPDR: Timer/counter 40 capture data register      | 228 |

|    |        | 14.2.5   | TIMER40 PREDR: Timer/counter 40 prescaler data register    | 228 |

|    |        | 14.2.6   | TIMER40_PREDR2: Timer/counter 40 prescaler data register 2 | 229 |

|    |        | 14.2.7   | TIMER40_CNT: Timer/counter 40 counter register             | 229 |

|    | 14.3   | Functio  | nal description                                            | 230 |

|    |        | 14.3.1   | Timer counter 40                                           | 230 |

|    |        | 14.3.2   | 16-bit timer/counter mode                                  | 230 |

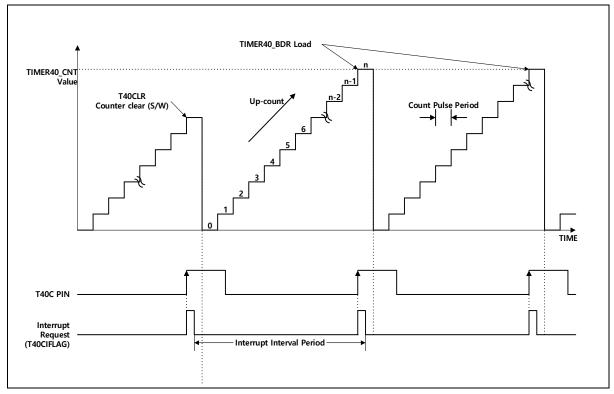

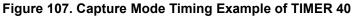

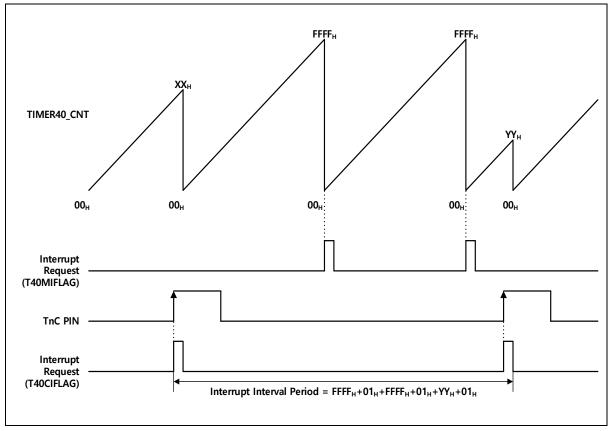

|    |        | 14.3.3   | 16-bit capture mode                                        | 233 |

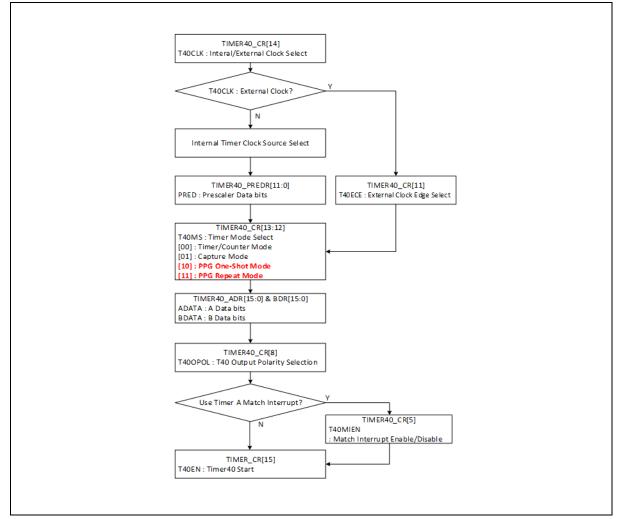

|    |        | 14.3.4   | 16-bit PPG mode                                            | 236 |

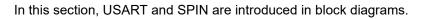

| 15 | Unive  | rsal syn | chronous/asynchronous receiver/transmitter                 | 239 |

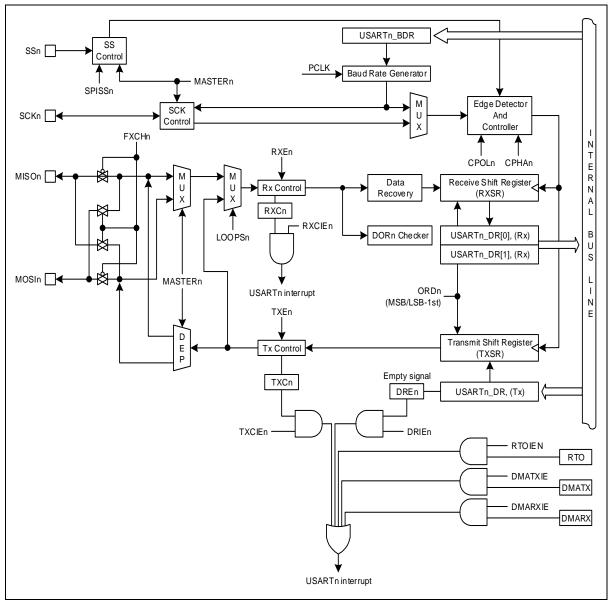

|    | 15.1   | USART    | ۲<br>block diagram                                         | 240 |

|    | 15.2   |          | ers                                                        |     |

|    |        | 15.2.1   | USARTn_CR1: USARTn control register 1                      | 242 |

|    |        |          | USARTn_CR2: USARTn control register 2                      |     |

|    |        | 15.2.3   | USARTn_ST: USARTn status register                          | 245 |

|    |        | 15.2.4   | USARTn_BDR: USARTn baud rate generation register           | 246 |

|    |        | 15.2.5   | USARTn_DR: USARTn data register                            | 247 |

|    |        | 15.2.6   | USARTn_FPCR: USARTn floating point count register          | 247 |

|    |        | 15.2.7   | USARTn_RTO: USARTn RTO register                            | 248 |

|    | 15.3   | Functio  | nal description                                            | 248 |

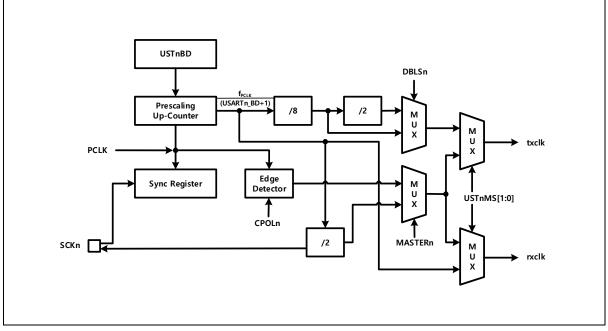

|    |        | 15.3.1   | USART clock generation                                     | 249 |

|    |        | 15.3.2   | External clock (SCKn)                                      | 250 |

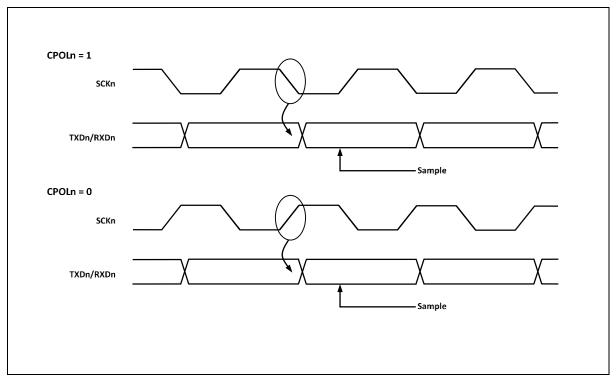

|    |        | 15.3.3   | Synchronous mode operation                                 | 250 |

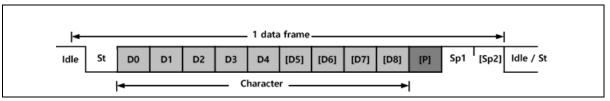

|    |        | 15.3.4   | UART data format                                           | 251 |

|    |        | 15.3.5   | UART parity bit                                            | 252 |

|    |        | 15.3.6   | UART transmitter                                           | 252 |

|    |        | 15.3.7   | UART receiver                                              | 254 |

|    |        | 15.3.8   | SPI mode                                                   | 257 |

|    |        | 15.3.9   | SPI clock formats and timing                               | 257 |

|    |        | 15.3.10  | )Baud rate settings (example)                              | 260 |

|    |        | 15.3.11  | 0% error baud rate                                         | 261 |

|    |        | 15.3.12  | Receive time out (RTO)                                     | 261 |

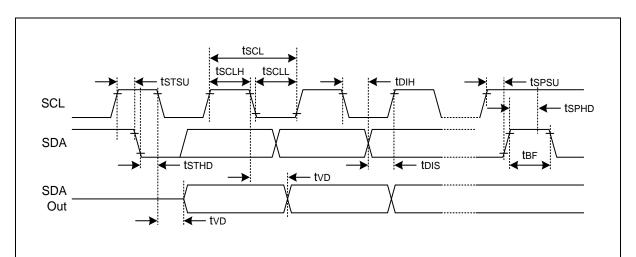

| 16 | I2C in | terface. |                                                            | 262 |

|    | 16.1   | I2C blo  | ck diagram                                                 | 263 |

|    | 16.2   | Registe  | ers                                                        | 263 |

|    |        | 16.2.1   | I2Cn_CR: I2Cn control register                             | 264 |

|    |        | 16.2.2   | I2Cn_ST: I2Cn status register                              | 265 |

|    |        |          | I2Cn_SAR1: I2Cn slave address register 1                   |     |

|    |        |          | I2Cn_SAR2: I2Cn slave address register 2                   |     |

|    |        |          | I2Cn_DR: I2Cn data register                                |     |

|    |        |          | I2Cn_SDAHR: I2Cn SDA hold time register                    |     |

|    |        | 16.2.7   | I2Cn_SCLLR: I2Cn SCL low period register                   | 268 |

|    |        |          |                                                            |     |

|    |        | 16.2.8  | I2Cn_SCLHR: I2Cn SCL high period register                                           | . 269 |

|----|--------|---------|-------------------------------------------------------------------------------------|-------|

|    |        | 16.2.9  | I2Cn_MR: I2Cn mode control register                                                 | . 269 |

|    | 16.3   | Functio | nal description                                                                     | .270  |

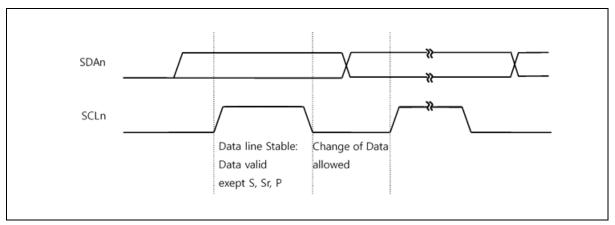

|    |        | 16.3.1  | I2C bit transfer                                                                    | .270  |

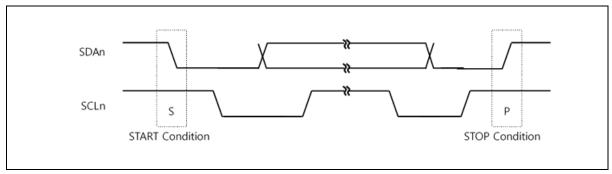

|    |        | 16.3.2  | START/repeated START/STOP                                                           | .270  |

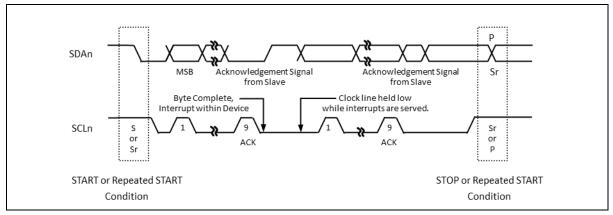

|    |        | 16.3.3  | Data transfer                                                                       | .271  |

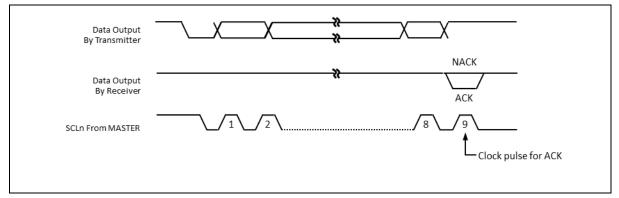

|    |        | 16.3.4  | Acknowledge                                                                         | .271  |

|    |        | 16.3.5  | Synchronization/Arbitration                                                         | .272  |

|    |        | 16.3.6  | I2C operation                                                                       | .273  |

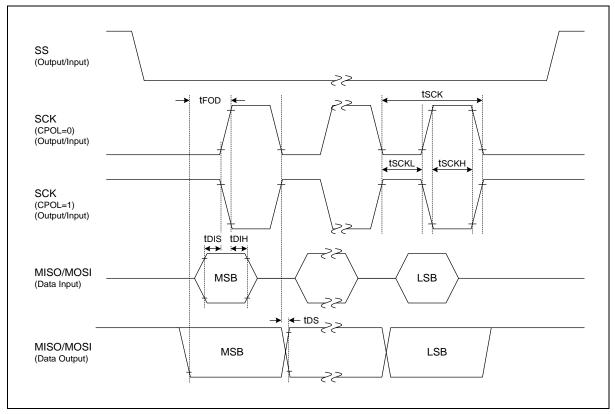

| 17 | Serial | periphe | ral interface (SPI)                                                                 | . 280 |

|    | 17.1   | SPI blo | ck diagram                                                                          | . 281 |

|    | 17.2   | -       | ers                                                                                 |       |

|    |        |         | SPIn.TDR: SPI transmit data register                                                |       |

|    |        |         | SPIn.RDR: SPI receive data register                                                 |       |

|    |        |         | SPIn.CR: SPI control register                                                       |       |

|    |        |         | SPIn.SR: SPI status register                                                        |       |

|    |        |         | SPIn.BR: SPI baud rate register                                                     |       |

|    |        |         | SPIn.EN: SPI enable register                                                        |       |

|    |        |         | SPIn.LR: SPI delay length register                                                  |       |

|    | 17.3   |         | nal description                                                                     |       |

|    |        |         | SPI timing                                                                          |       |

|    |        |         | DMA handshake                                                                       |       |

| 18 |        |         |                                                                                     |       |

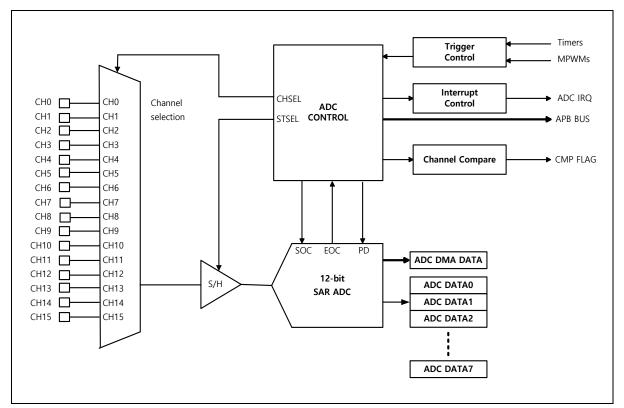

|    | 18.1   |         | ADC block diagram                                                                   |       |

|    | 18.2   | •       |                                                                                     |       |

|    |        |         | ADC_MR: ADC mode register                                                           |       |

|    |        |         | ADC_CSCR: ADC current sequence/channel register                                     |       |

|    |        |         | ADC_CCR: ADC clock control register                                                 |       |

|    |        |         | ADC_TRG: ADC trigger selection register                                             |       |

|    |        |         | ADC_SCSR1: ADC channel selection 1 register                                         |       |

|    |        |         | ADC_SCSR2: ADC channel selection 2 register                                         |       |

|    |        |         | ADC_CR: ADC control register                                                        |       |

|    |        |         | ADC_SR: ADC state register<br>ADC_IER: ADC interrupt enable register                |       |

|    |        |         |                                                                                     |       |

|    |        |         | ADC_DDR: ADC DMA data register                                                      |       |

|    |        |         | ADC_DR: ADC sequence 0 to 7 data register<br>ADC_CMPR: ADC channel compare register |       |

|    | 18.3   |         | nal description                                                                     |       |

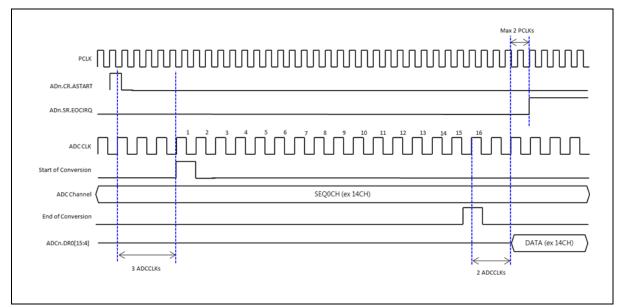

|    | 10.5   |         | ADC single mode timing diagram                                                      |       |

|    |        |         | ADC single mode timing diagram                                                      |       |

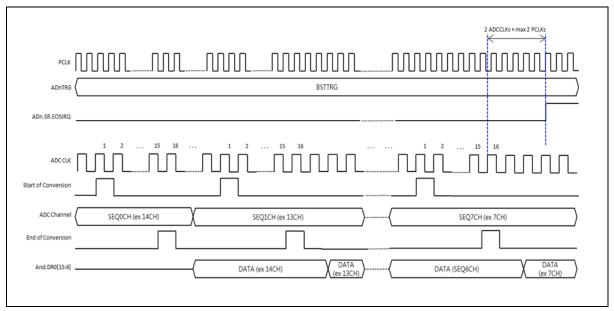

|    |        |         | ADC sequential mode timing diagram                                                  |       |

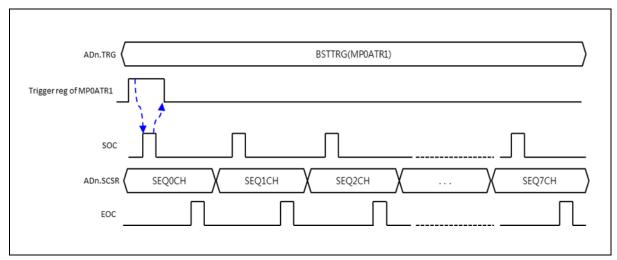

|    |        |         | ADC multiple mode timing diagram                                                    |       |

| 19 | 10-hit |         |                                                                                     |       |

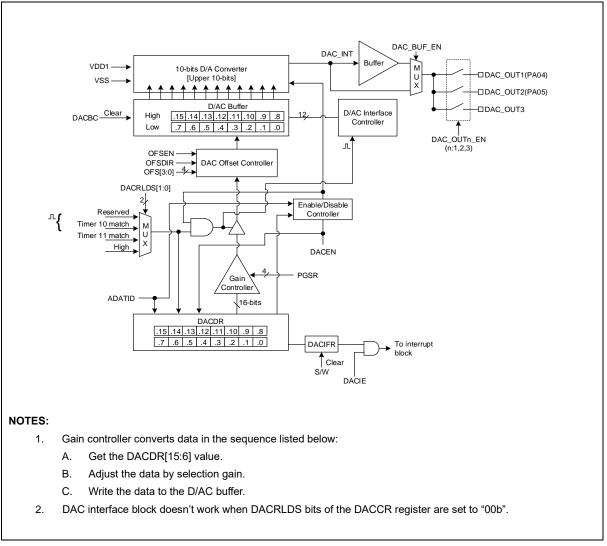

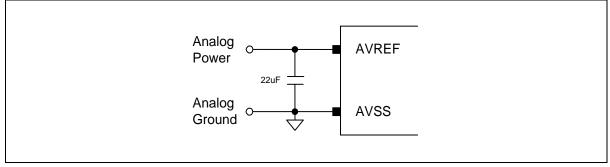

| 10 | 19.1   |         | DAC block diagram and analog power pin                                              |       |

|    | 19.2   |         | ers                                                                                 |       |

|    | 10.2   | -       | DAC_DR: DAC data register                                                           |       |

|    |        |         | DAC_BR: DAC buffer register                                                         |       |

|    |        |         | DAC_CR: DAC control register                                                        |       |

|    |        |         | DAC_PGSR: Programmable gain control register                                        |       |

|    |        |         | DAC_OFSCR: DAC offset control register                                              |       |

|    |        |         |                                                                                     |       |

|    | 19.3   | Functional description                                             | 313 |

|----|--------|--------------------------------------------------------------------|-----|

|    |        | 19.3.1 DAC data buffer register                                    |     |

|    |        | 19.3.2 Automatic DAC data increment/decrement                      | 313 |

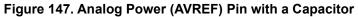

|    |        | 19.3.3 Programmable gain controller                                | 314 |

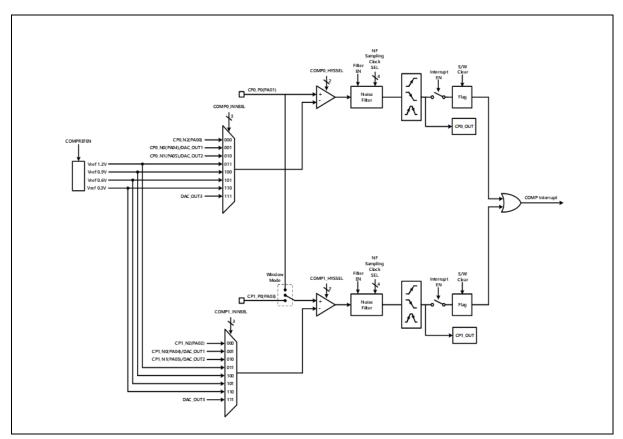

| 20 | Comp   | parator                                                            |     |

|    | 20.1   | Comparator block diagram                                           |     |

|    | 20.2   | Registers                                                          |     |

|    |        | 20.2.1 COMP0CR: Comparator 0 control register                      |     |

|    |        | 20.2.2 COMP1CR: Comparator 1 control register                      |     |

|    |        | 20.2.3 COMPDBNC: Comparator debounce register                      |     |

|    |        | 20.2.4 COMPICON: Comparator Interrupt control register             |     |

|    |        | 20.2.5 COMPIEN: Comparator interrupt enable register               |     |

|    |        | 20.2.6 COMPIST: Comparator interrupt status register               |     |

|    |        | 20.2.7 COMPICLR: Comparator interrupt clear register               |     |

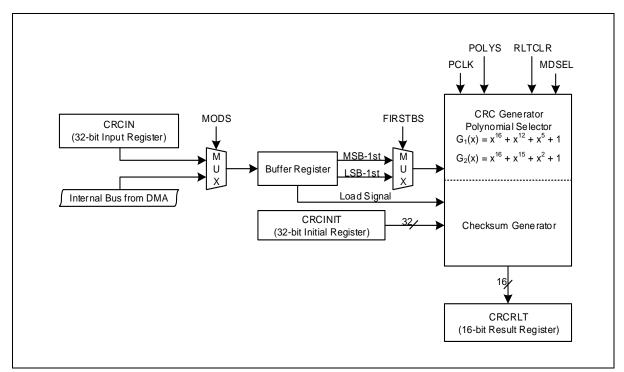

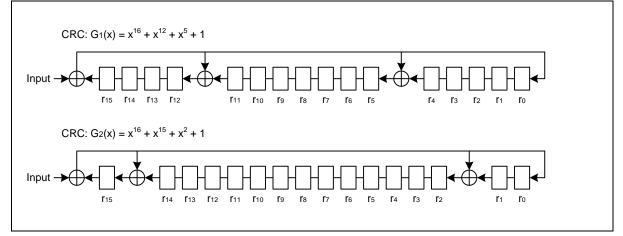

| 21 | Cyclic | c redundancy check and checksum (CRC checksum)                     |     |

|    | 21.1   | CRC and checksum block diagram                                     |     |

|    | 21.2   | Registers                                                          |     |

|    |        | 21.2.1 CRC_CR: CRC control register                                |     |

|    |        | 21.2.2 CRC_IN: CRC input data register                             |     |

|    |        | 21.2.3 CRC_RLT: CRC result data register                           |     |

|    |        | 21.2.4 CRC_INIT: CRC initial data register                         |     |

|    | 21.3   | Functional description                                             |     |

|    |        | 21.3.1 CRC polynomial structure                                    |     |

|    |        | 21.3.2 CRC operation procedure in DMA mode                         |     |

|    |        | 21.3.3 CRC operation procedure in user CRC and checksum mode       |     |

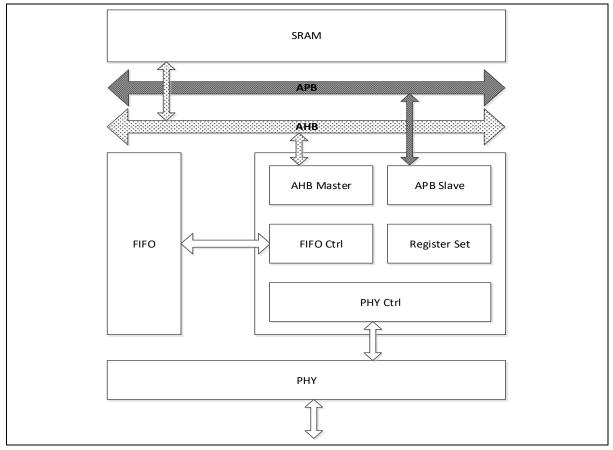

| 22 |        | full speed device interface                                        |     |

|    | 22.1   | USB block diagram                                                  |     |

|    | 22.2   | Registers                                                          |     |

|    |        | 22.2.1 GOTGCTL: Control and status register                        |     |

|    |        | 22.2.2 GOTGINT: Interrupt register                                 |     |

|    |        | 22.2.3 GAHBCFG: AHB configuration register                         |     |

|    |        | 22.2.4 GUSBCFG: USB configuration register                         |     |

|    |        | 22.2.5 GRSTCTL: Reset register                                     |     |

|    |        | 22.2.6 GINTSTS: Interrupt register                                 |     |

|    |        | 22.2.7 GINTMSK: Interrupt mask register                            |     |

|    |        | 22.2.8 GRXSTSR: Receive status debug read register                 |     |

|    |        | 22.2.9 GRXSTSP: Receive status read/pop register                   |     |

|    |        | 22.2.10 GRXFSIZ: Receive FIFO size register                        |     |

|    |        | 22.2.11 GNPTXFSIZ: Non-periodic transmit FIFO size register        |     |

|    |        | 22.2.12 GHWCFG1: User HW config1 register                          |     |

|    |        | 22.2.13 GHWCFG2: User HW config2 register                          |     |

|    |        | 22.2.14 GHWCFG3: User HW config2 register                          |     |

|    |        | 22.2.15 GHWCFG4: User hardware config4 register                    |     |

|    |        | 22.2.16 GLPMCFG: LPM config register                               |     |

|    |        | 22.2.17 GPWRDN: Global power down register                         |     |

|    |        | 22.2.18 GDFIFOCFG: Global DFIFO configuration register             |     |

|    |        | 22.2.19 DIEPTXFi: Device IN endpoint transmit FIFO size register i |     |

|    |        | 22.2.20 DCFG: Device configuration register                        |     |

|    |        | 22.2.21 DCTL: Device control register                              |     |

|    |        | 22.2.22 DSTS: Device status register                               |     |

|        | 22.2.23 DIEPMSK: Device IN endpoint common interrupt mask register        | 369 |

|--------|---------------------------------------------------------------------------|-----|

|        | 22.2.24 DOEPMSK: Device OUT endpoint common interrupt mask register       | 370 |

|        | 22.2.25 DAINT: Device all endpoints interrupt register                    | 372 |

|        | 22.2.26 DAINTMSK: Device all endpoints interrupt mask register            | 373 |

|        | 22.2.27 DTHRCTL: Device threshold control register                        | 374 |

|        | 22.2.28 DIEPEMPMSK: Device IN endpoint FIFO empty interrupt mask register | 376 |

|        | 22.2.29 DIEPCTL0: Device control IN endpoint 0 control register           | 376 |

|        | 22.2.30 DIEPINT0: Device IN endpoint 0 interrupt register                 | 378 |

|        | 22.2.31 DIEPDMA0: Device IN endpoint 0 DMA address register               | 380 |

|        | 22.2.32 DTXFSTS0: Device IN endpoint transmit FIFO status register 0      | 381 |

|        | 22.2.33 DIEPDMAB0: Device IN endpoint 16 buffer address register          | 381 |

|        | 22.2.34 DIEPCTLi : Device control IN endpoint i control register          | 382 |

|        | 22.2.35 DIEPINTi: Device IN endpoint I interrupt register                 | 385 |

|        | 22.2.36 DIEPDMAi: Device IN endpoint I DMA address register               | 387 |

|        | 22.2.37 DTXFSTSi: Device IN endpoint transmit FIFO status register i      | 388 |

|        | 22.2.38 DIEPDMABi: Device IN endpoint I buffer address register           | 388 |

|        | 22.2.39 DOEPCTL0: Device control OUT endpoint 0 control register          | 389 |

|        | 22.2.40 DOEPINT0: Device OUT endpoint 0 interrupt register                | 391 |

|        | 22.2.41 DOEPDMA0: Device OUT endpoint 0 DMA address register              |     |

|        | 22.2.42 DOEPDMAB0: Device OUT Endpoint 16 Buffer Address Register         |     |

|        | 22.2.43 DOEPCTLi: Device control OUT endpoint I control register          |     |

|        | 22.2.44 DOEPINTi: Device OUT endpoint I interrupt register                |     |

|        | 22.2.45 DOEPDMAi: Device OUT Endpoint I DMA Address Register              |     |

|        | 22.2.46 DOEPDMABi: Device OUT Endpoint I Buffer Address Register          |     |

|        | 22.2.47 PCGCCTL: Power and Clock Gating Control Register                  |     |

| 22.3   | Functional description                                                    | 403 |

|        | 22.3.1 USB device                                                         | 403 |

|        | 22.3.2 USB descriptors                                                    | 405 |

|        | 22.3.3 USB operation                                                      |     |

|        | 22.3.4 USB transfer                                                       |     |

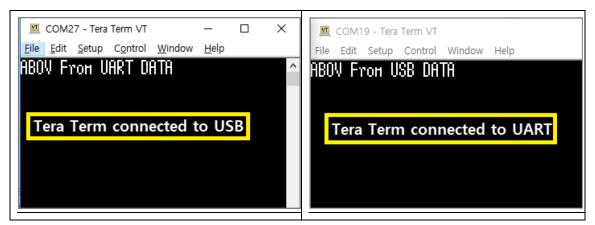

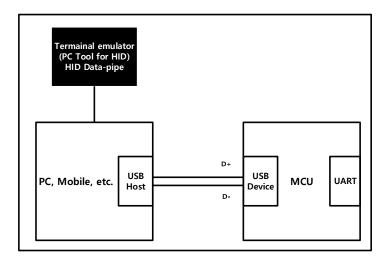

|        | 22.3.5 USB software example                                               | 409 |

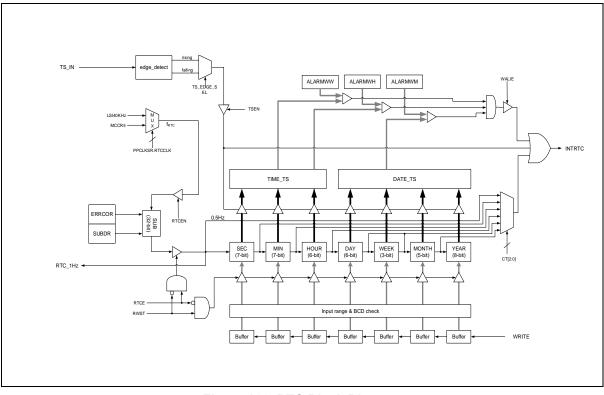

| Real-t | ime clock (RTC)                                                           | 413 |

| 23.1   | RTC block diagram                                                         |     |

| 23.2   | Registers                                                                 | 415 |

|        | 23.2.1 RTCCR: RTC control register                                        |     |

|        | 23.2.2 ERRCOR: Error correction register                                  |     |

|        | 23.2.3 SEC: Second counter register                                       |     |

|        | 23.2.4 MIN: Minute counter register                                       |     |

|        | 23.2.5 HOUR: Hour counter register                                        |     |

|        | 23.2.6 DAY: Day counter register                                          |     |

|        | 23.2.7 WEEK: Week counter register                                        |     |

|        | 23.2.8 MONTH: Month counter register                                      |     |

|        | 23.2.9 YEAR: Year counter register                                        |     |

|        | 23.2.10 ALARMW: Alarm register                                            |     |

|        | 23.2.11 SUBDR: Sub-second counter compare register                        |     |

|        | 23.2.12 TIME_TS: TimeStamp time register                                  |     |

|        | 23.2.13 DATE_TS: TimeStamp date register                                  |     |

|        | 23.2.14 BKUPDR: Backup register 1 to 4                                    |     |

|        | 23.2.15 RTCPFCR: RTC pin function configuration register                  |     |

| 23.3   | Functional description                                                    |     |

23

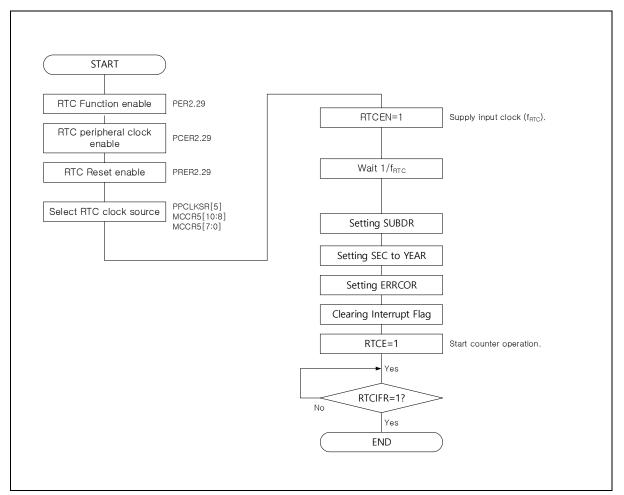

|          |              | 23.3.1 Starting the RTC Operation                               |     |

|----------|--------------|-----------------------------------------------------------------|-----|

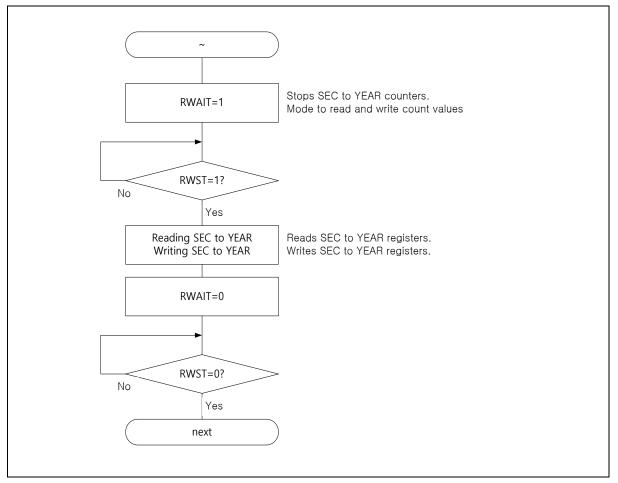

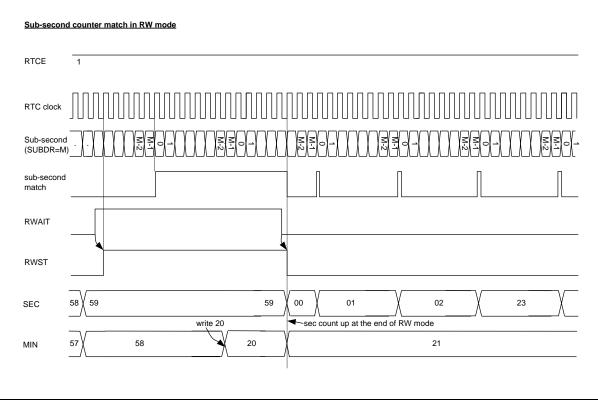

|          |              | 23.3.2 RTC RW mode (read and write mode)                        | 428 |

|          |              | 23.3.3 RTC alarm setting                                        | 431 |

|          |              | 23.3.4 RTC Constant-period matching                             | 432 |

|          |              | 23.3.5 RTC Timestamp                                            |     |

|          |              | 23.3.6 RTC 1Hz output                                           |     |

|          |              | 23.3.7 Error correction of RTC                                  |     |

|          |              | 23.3.8 BKUPDR and RTCPFCR registers                             |     |

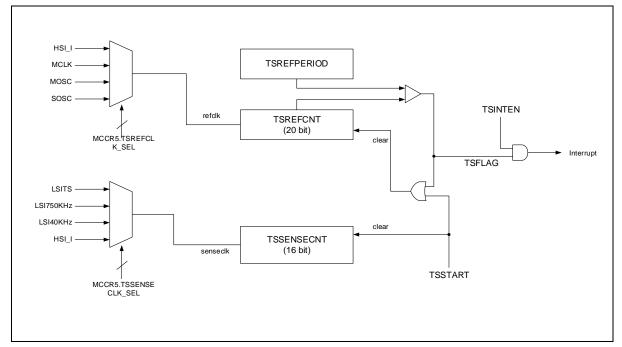

| 24       | Temp         | sensor                                                          |     |

|          | 24.1         | Temp sensor block diagram                                       | 437 |

|          | 24.2         | Registers                                                       |     |

|          |              | 24.2.1 TSENSECON: Temp sensor control register                  |     |

|          |              | 24.2.2 TSREFPEROID: Temp sensor reference clock period register |     |

|          |              | 24.2.3 TSSENSECNT: Temp sensor sense clock count register       | 439 |

|          | 24.3         | Functional discription                                          |     |

|          |              | 24.3.1 How to calculate and convert to temperature              |     |

| 25       |              | ical characteristics                                            |     |

|          | 25.1         | Absolute maximum ratings                                        |     |

|          | 25.2         | Recommended operating conditions                                |     |

|          | 25.3         | ADC characteristics                                             |     |

|          | 25.4         | DAC characteristics                                             |     |

|          | 25.5         | Power on reset characteristics                                  |     |

|          | 25.6         | Low voltage reset/indicator characteristics                     |     |

|          | 25.7         | High frequency internal RC oscillator characteristics           |     |

|          | 25.8         | Low frequency internal RC oscillator characteristics            |     |

|          | 25.9         | DC electrical characteristics                                   |     |

|          |              | Supply current characteristics                                  |     |

|          |              | AC characteristics                                              |     |

|          |              | USART SPI characteristics                                       |     |

|          |              | I2C characteristics                                             |     |

|          |              | USART UART timing characteristics                               |     |

|          |              | Data retention voltage in STOP mode                             |     |

|          |              | Internal Flash ROM characteristics                              |     |

|          |              | Main oscillator characteristics                                 |     |

|          |              | Sub oscillator characteristics                                  |     |

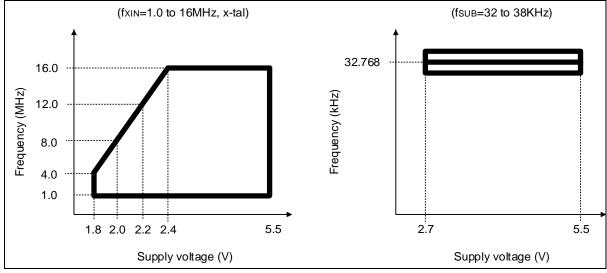

|          |              | Operating voltage range                                         |     |

|          |              | PLL electrical characteristics                                  |     |

|          |              | Comparator characteristics                                      |     |

|          |              | USB characteristics                                             |     |

| 26       |              | Temperature Sensor characteristics<br>opment tools              |     |

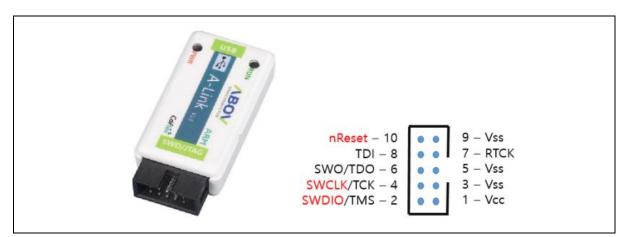

| 20       | 26.1         | •                                                               |     |

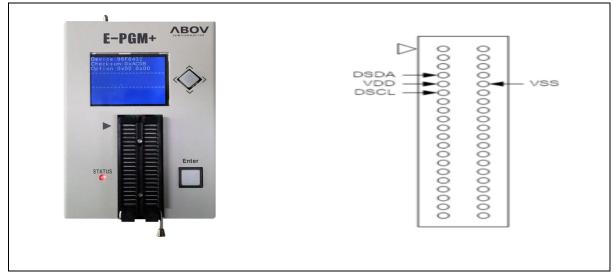

|          | 26.1         | Compiler                                                        |     |

|          | 26.2         | Debugger                                                        |     |

| 27       |              | Programmer                                                      |     |

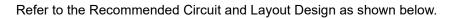

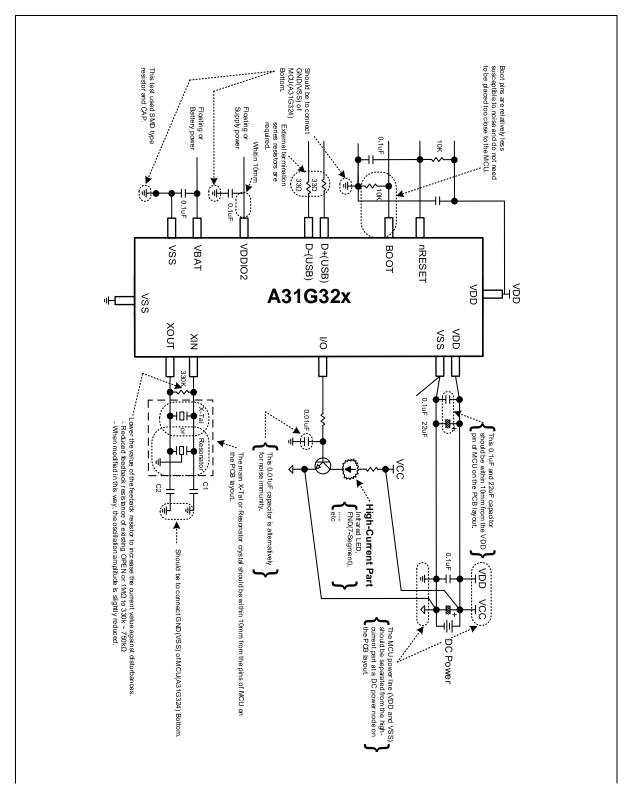

| 27<br>28 |              | t Design Guide<br>age information                               |     |

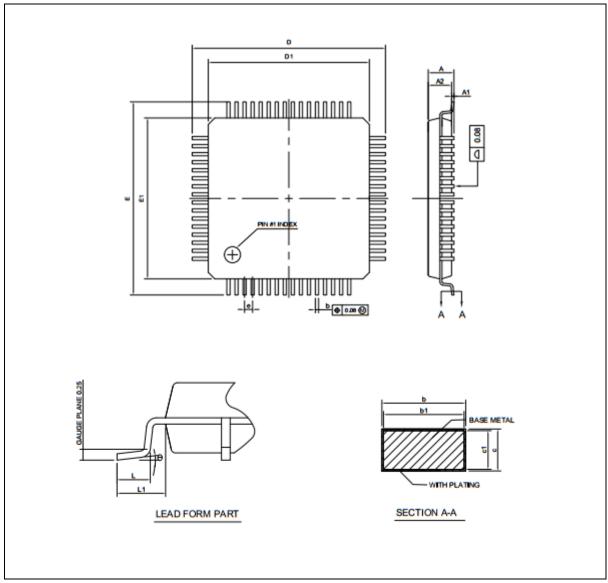

| 20       | 28.1         | 64 LQFP package information                                     |     |

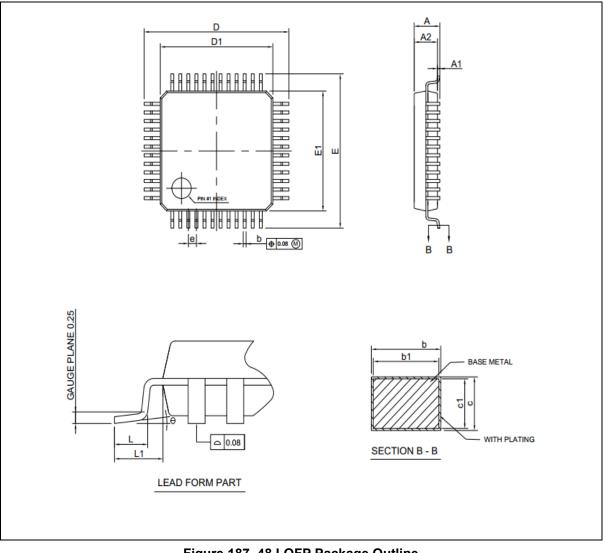

|          | 20.1<br>28.2 | 48 LQFP package information                                     |     |

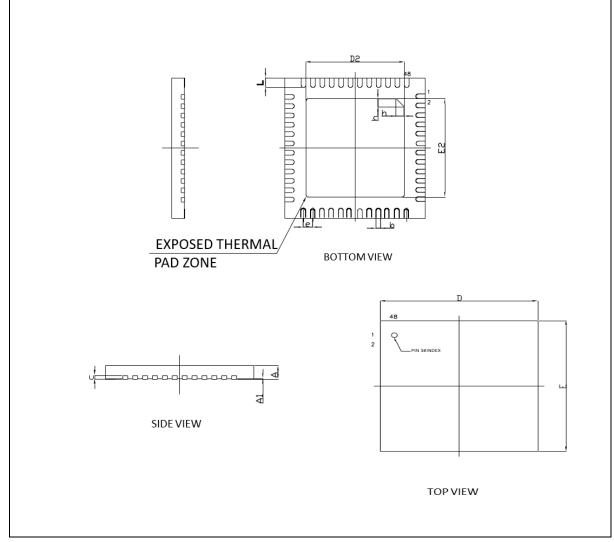

|          | 20.2<br>28.3 | 48 QFN package information                                      |     |

| 29       |              | ing information                                                 |     |

| 23       | Ordel        |                                                                 | +/0 |

| evision history471 |

|--------------------|

|--------------------|

## List of figures

| Figure 1. A31G32x Block diagram                                      | 22  |

|----------------------------------------------------------------------|-----|

| Figure 2. LQFP 64 Pinouts                                            | 23  |

| Figure 3. LQFP 48 Pinouts                                            | 24  |

| Figure 4. QFN 48 Pinouts                                             | 25  |

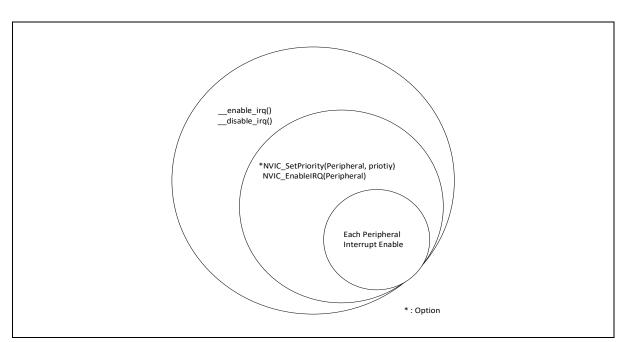

| Figure 5. Interrupt Block Diagram                                    | 37  |

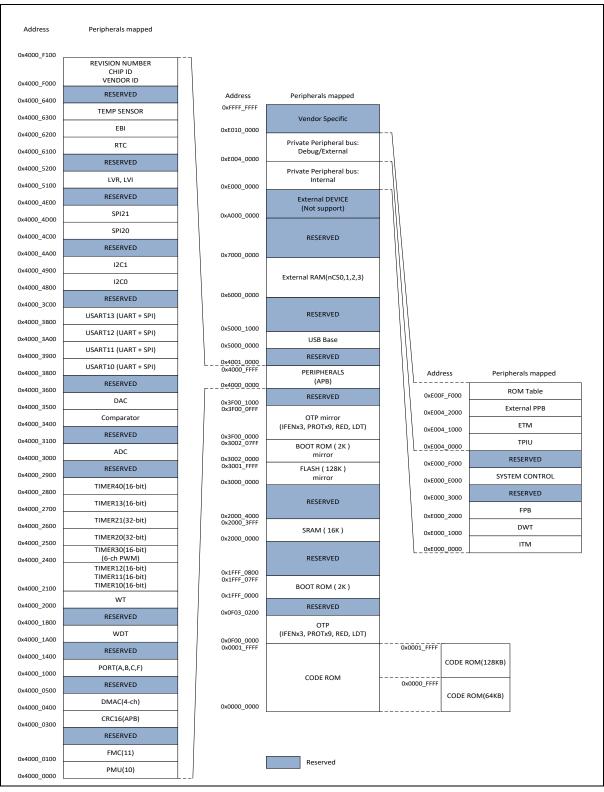

| Figure 6. Memory Map                                                 | 39  |

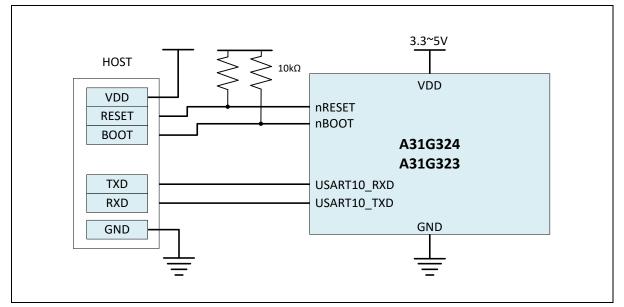

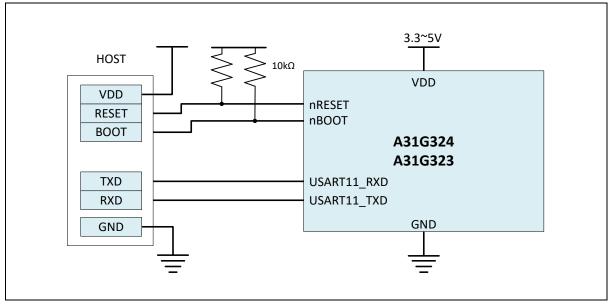

| Figure 7. Connection Diagram of UART10 Boot                          | 41  |

| Figure 8. Connection Diagram of UART11 Boot                          | 41  |

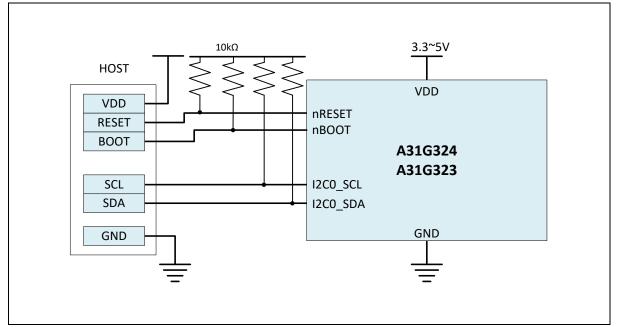

| Figure 9. Connection Diagram of I2C Boot                             | 42  |

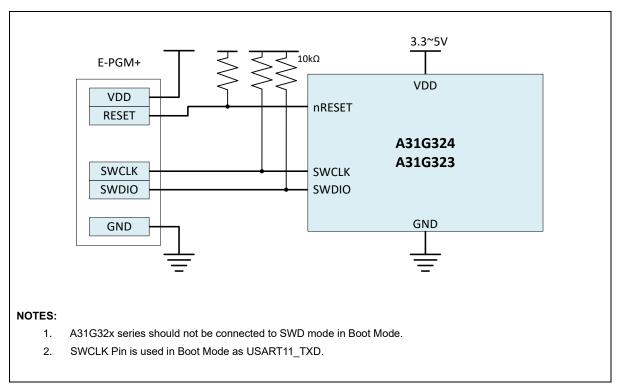

| Figure 10. Connection Diagram of E-PGM+ and SWD Port                 | 42  |

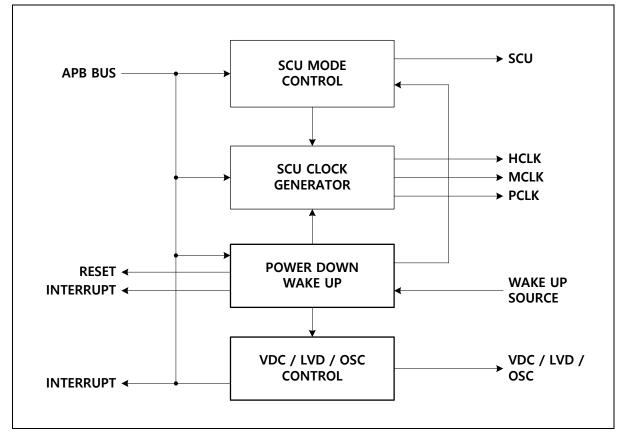

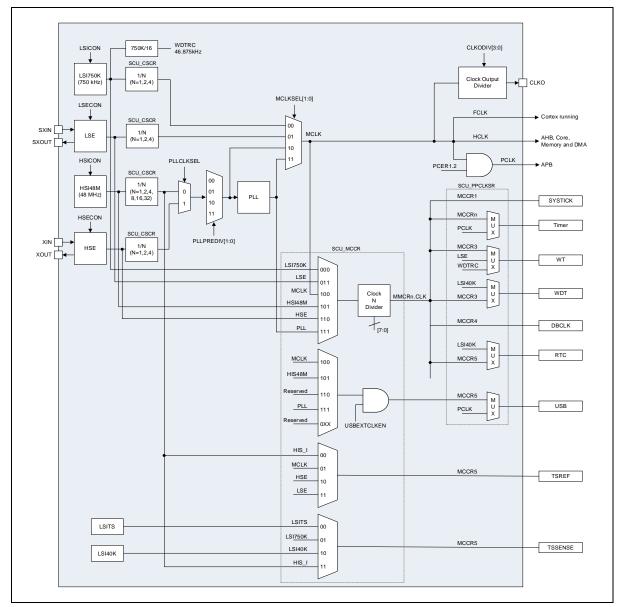

| Figure 11. SCU Block diagram                                         | 43  |

| Figure 12. Clock Tree Configuration                                  | 44  |

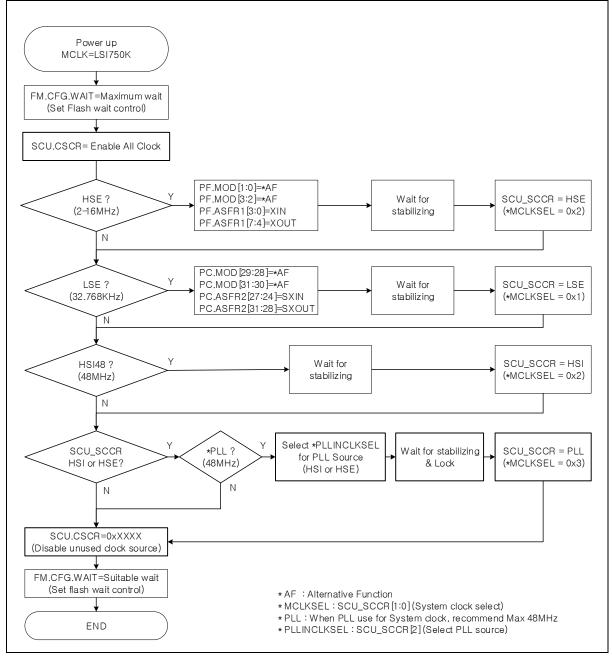

| Figure 13. Clock Change Procedure                                    | 46  |

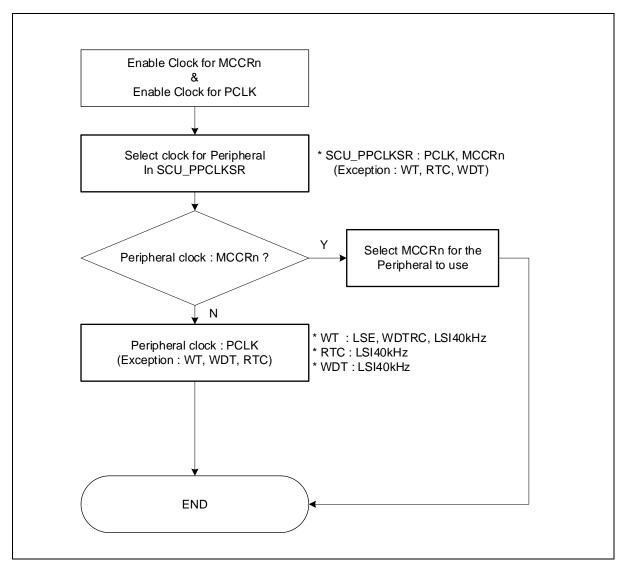

| Figure 14. Peripheral Clock Select (n: 1, 2, 3, 4, 5, and 6)         | 47  |

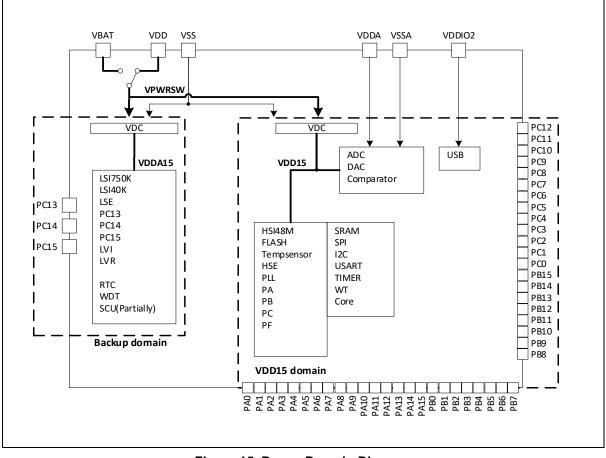

| Figure 15. Power Domain Diagram                                      | 49  |

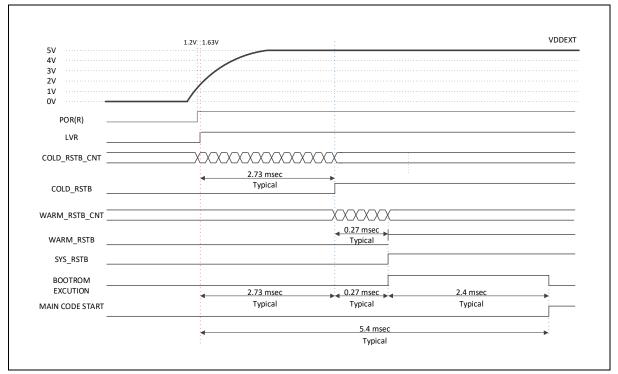

| Figure 16. Power up Procedure                                        | 50  |

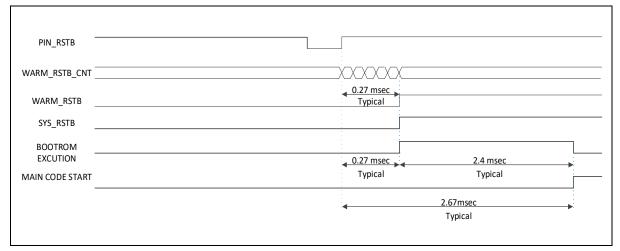

| Figure 17. Warm Reset Diagram                                        | 51  |

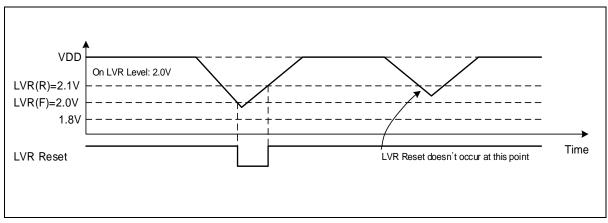

| Figure 18. LVR Reset Timing Diagram                                  | 51  |

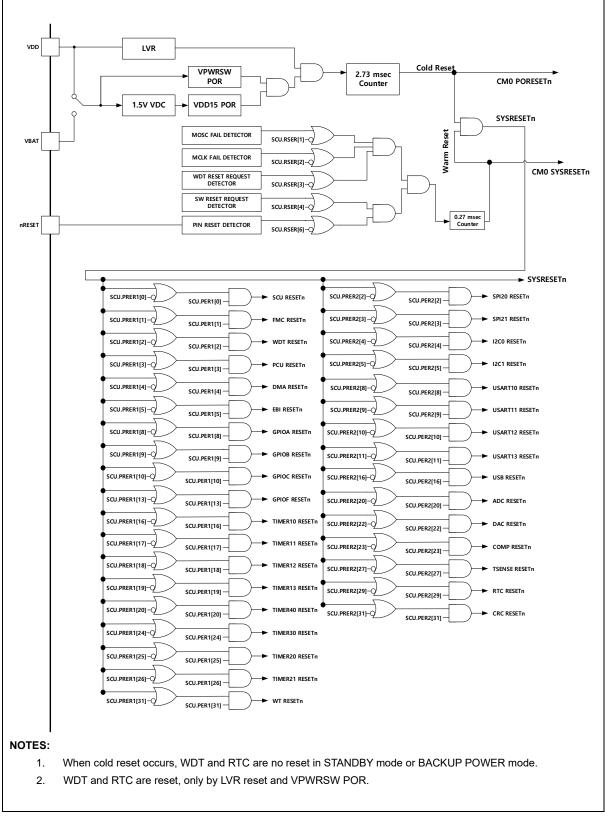

| Figure 19. Reset Tree Configuration                                  | 52  |

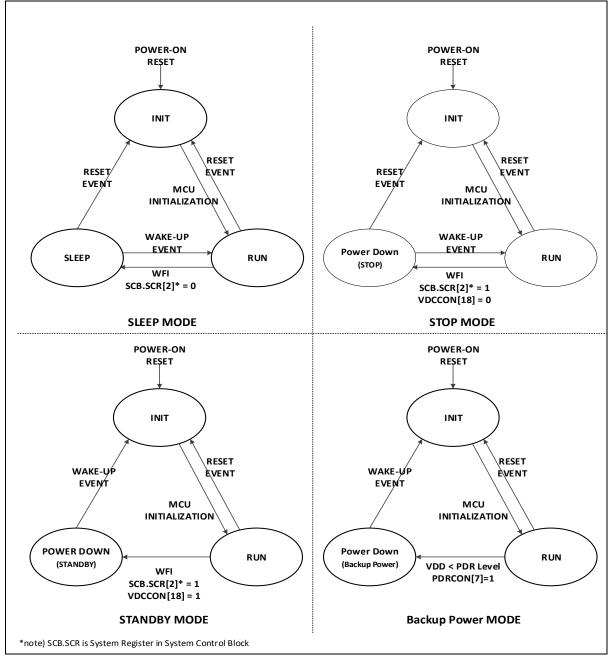

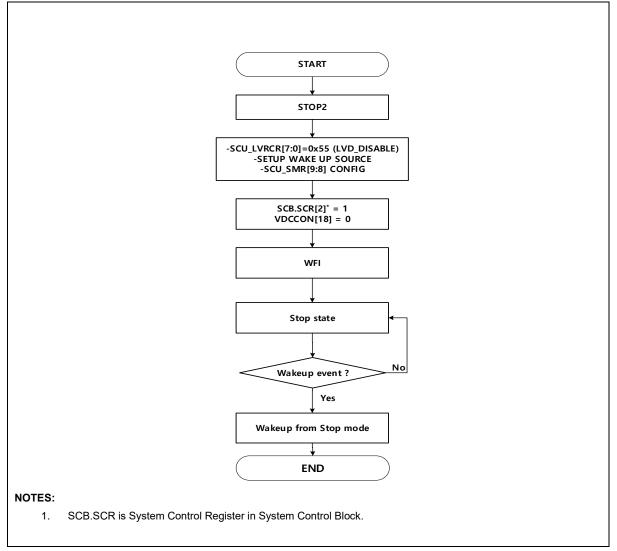

| Figure 20. Transition between Operation Modes                        | 53  |

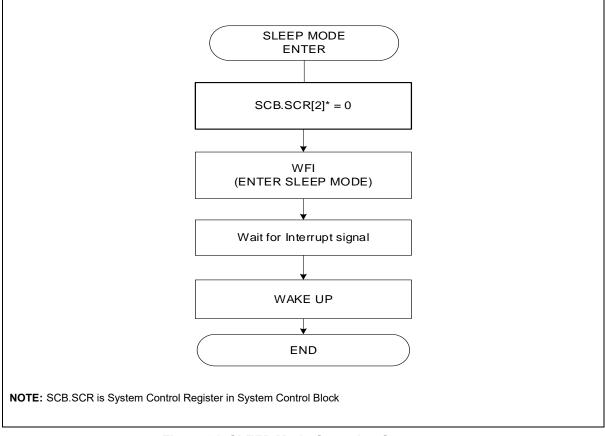

| Figure 21. SLEEP Mode Operation Sequence                             | 54  |

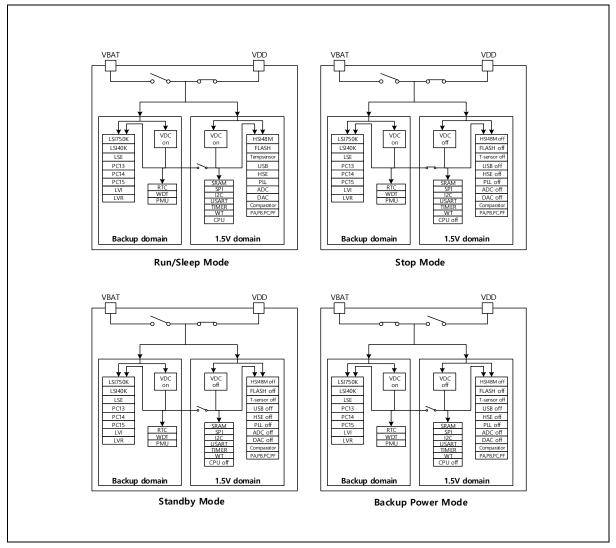

| Figure 22. Power down Mode Block Diagram                             | 55  |

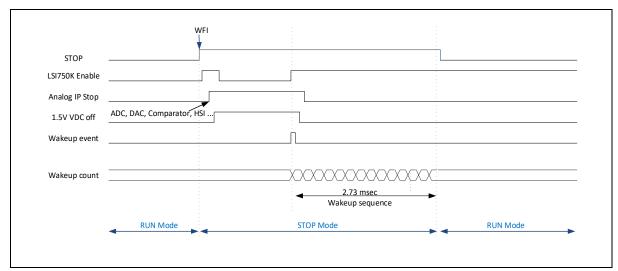

| Figure 23. STOP Mode Sequence                                        | 58  |

| Figure 24. STOP Mode Timing Diagram                                  | 58  |

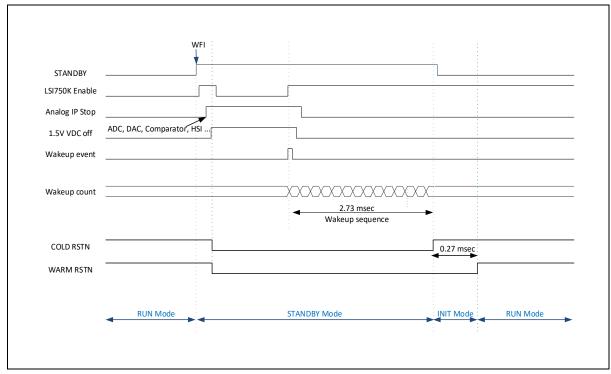

| Figure 25. STANDBY Mode Sequence                                     | 59  |

| Figure 26. STANDBY Mode Timing Diagram                               | 60  |

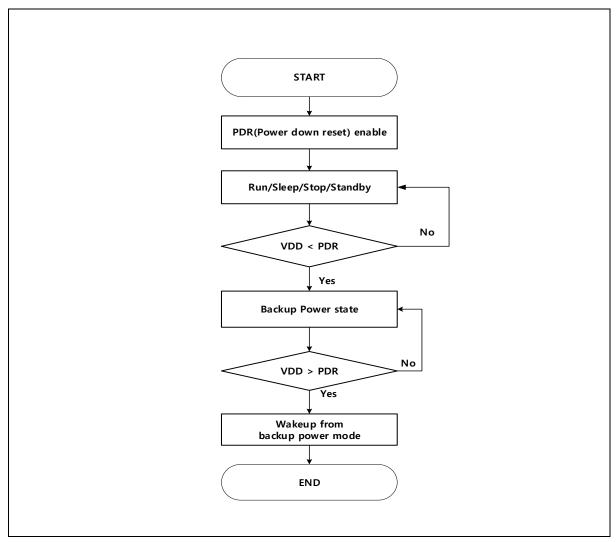

| Figure 27. BACKUP POWER Mode Sequence                                | 61  |

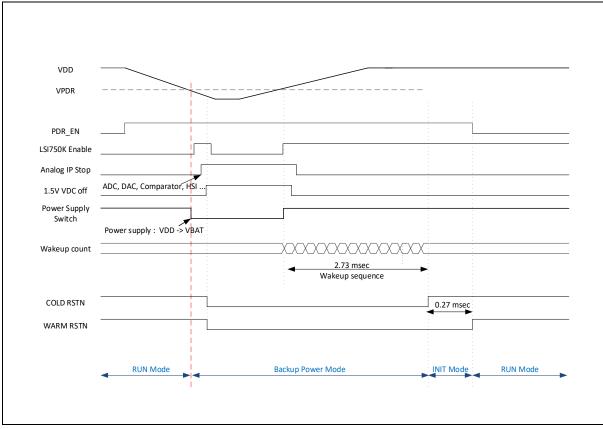

| Figure 28. BACKUP POWER Mode Timing Diagram                          | 62  |

| Figure 29. LVI Block Diagram                                         | 99  |

| Figure 30. LVR Block Diagram                                         | 99  |

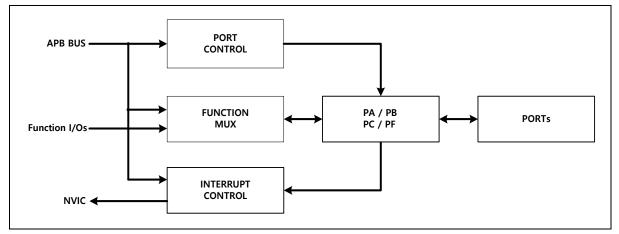

| Figure 31. PCU Block Diagram                                         | 101 |

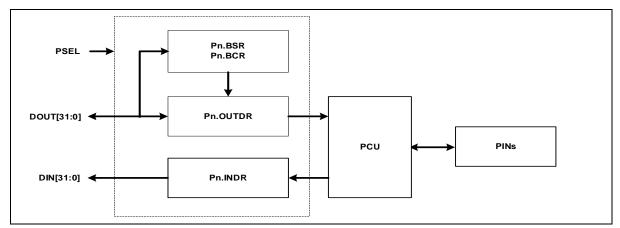

| Figure 32. GPIO Block Diagram(Except PC13, PC14, PC15)               | 102 |

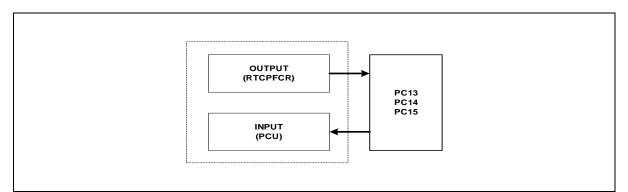

| Figure 33. PC13, PC14, PC15 Block Diagram                            | 102 |

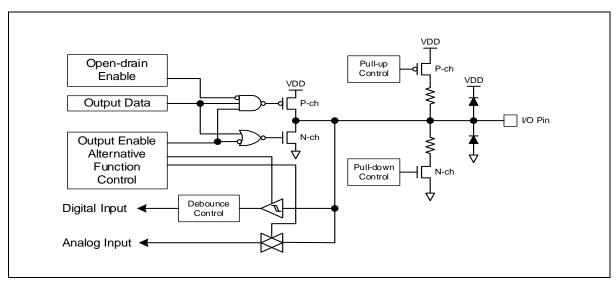

| Figure 34. I/O Port Block Diagram (External Interrupt I/O Pins)      | 102 |

| Figure 35. Port Diagram                                              | 116 |

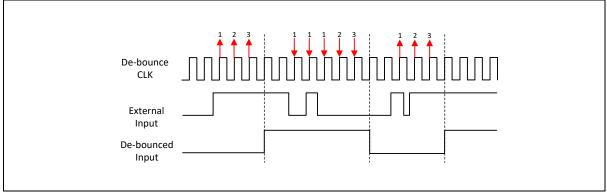

| Figure 36. Debounce Function Timing Diagram                          | 117 |

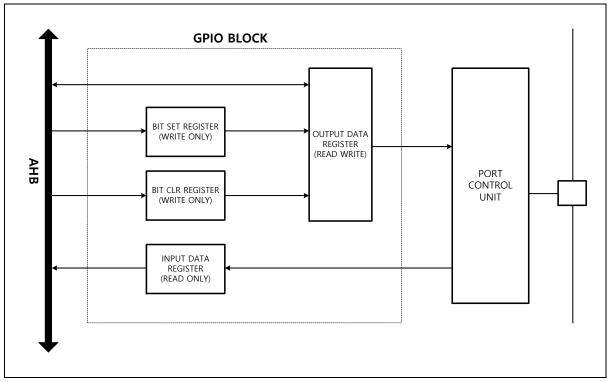

| Figure 37. GPIO Diagram                                              | 117 |

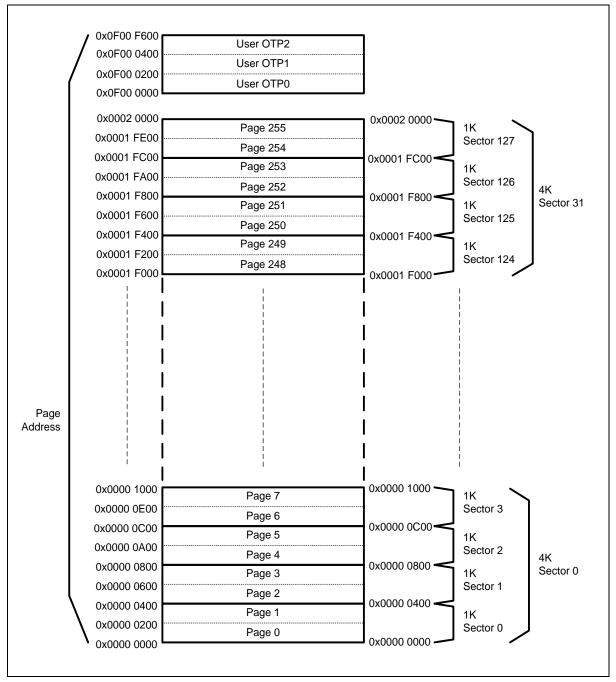

| Figure 38. Flash Memory Map (128 KB Code Flash)                      | 119 |

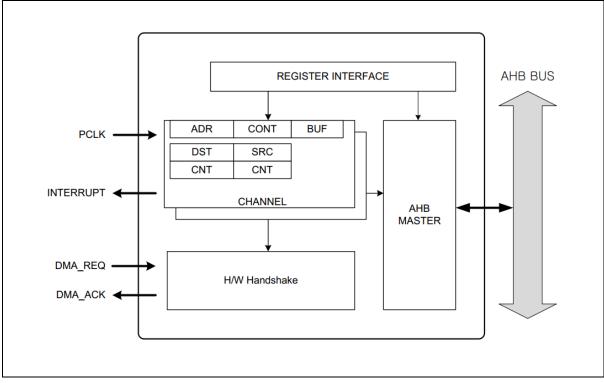

| Figure 39. DMAC Block Diagram                                        | 129 |

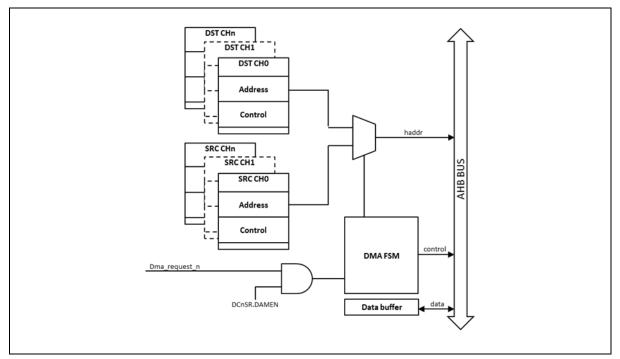

| Figure 40. DMAC Functional Block Diagram                             | 135 |

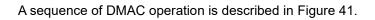

| Figure 41. DMAC Operation Sequence                                   | 136 |

| Figure 42. Timing Diagram of DMAC Transfer from Peripheral to Memory | 137 |

| Figure 43. Timing Diagram of DMAC Transfer from Memory to Peripheral | 137 |

| Figure 44. Timing Diagram Example of N DMAC Transfer                 |     |

| Figure 45. Static Memory Controller Block Diagram                    |     |

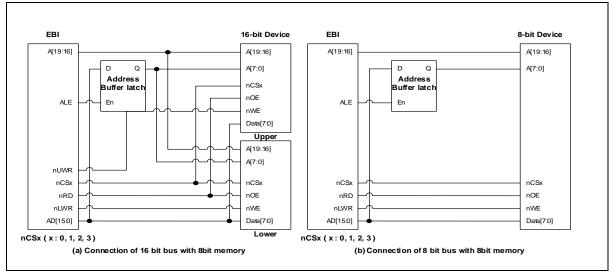

| Figure 46. Bus Configuration with 8-bit Memory                       | 142 |

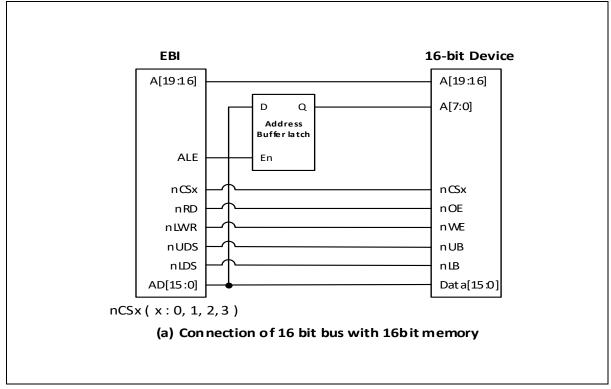

| Figure 47. Bus Configuration with 16-bit Memory                      | 143 |

|                                                                      |     |

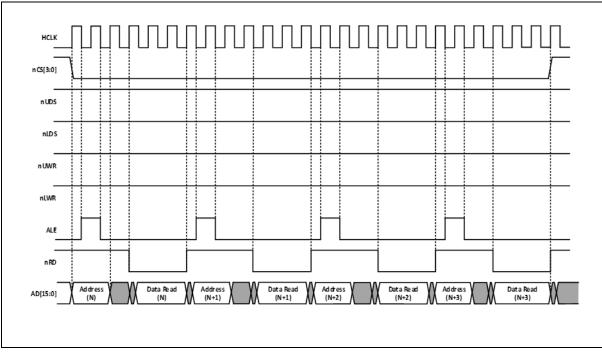

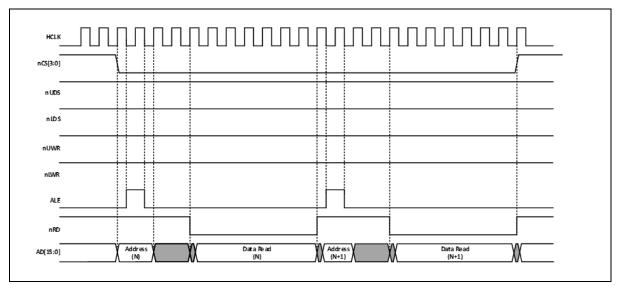

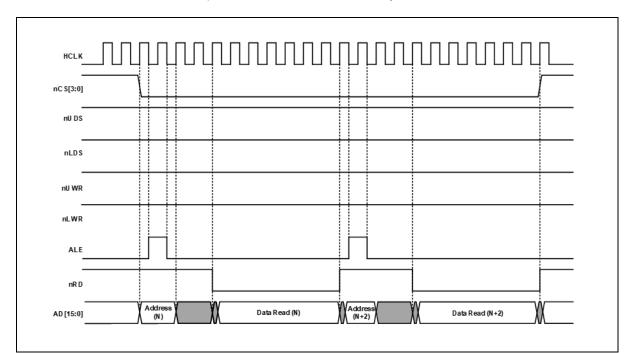

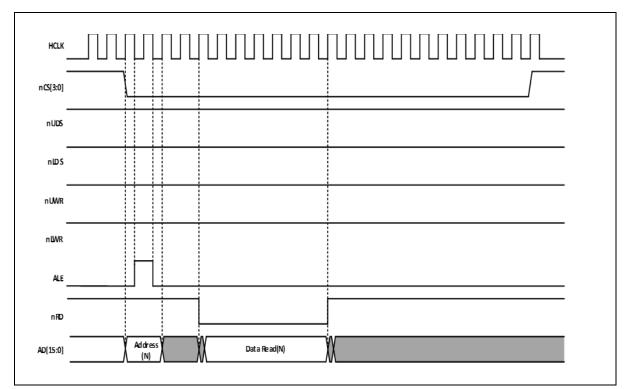

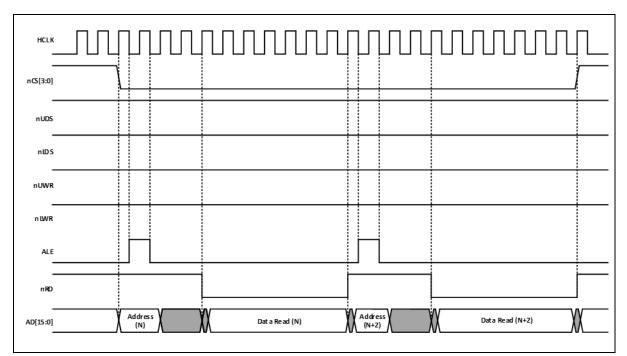

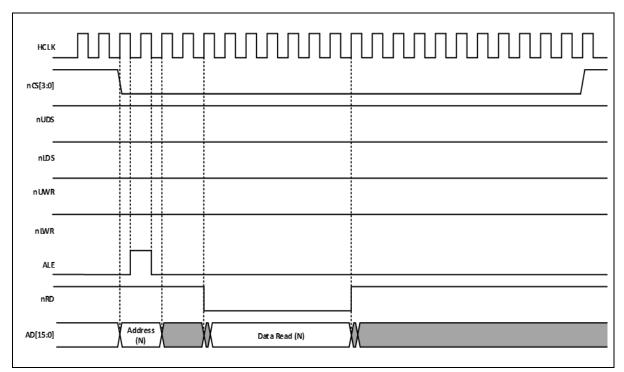

| Figure 48. | Word Read Operation with 8-bit Memory and 8-bit Bus                     | . 144 |

|------------|-------------------------------------------------------------------------|-------|

| Figure 49. | Half Word Read Operation with 8-bit Memory and 8-bit Bus                | . 144 |

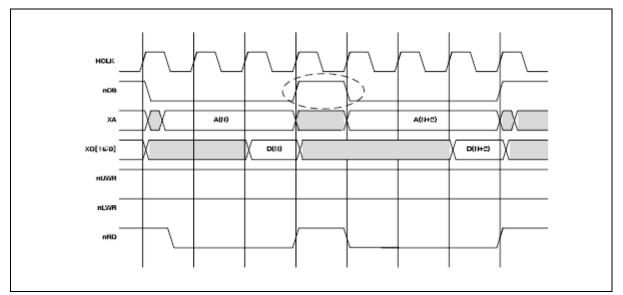

| Figure 50. | Word Read Operation with 8-bit Memory and 16-bit Bus                    | . 145 |

| Figure 51. | Half Word Read Operation with 8-bit Memory and 16-bit Bus               | . 145 |

| Figure 52. | Word Read Operation with 16-bit Memory and 16-bit Bus                   | . 146 |

| Figure 53. | Half Word Read Operation with 16-bit Memory and 16-bit Bus              | . 146 |

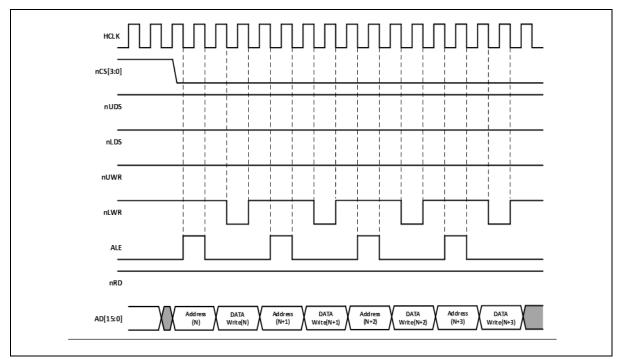

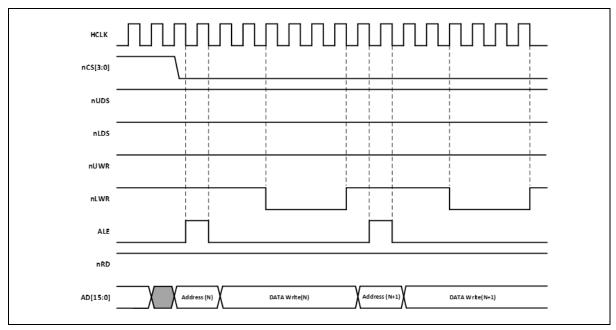

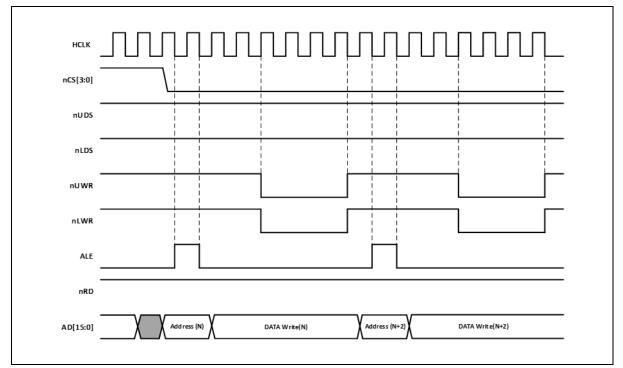

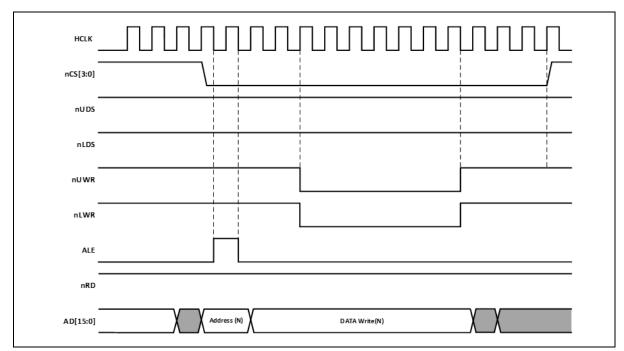

|            | Word Write Operation with 8-bit Memory and 8-bit Bus                    |       |

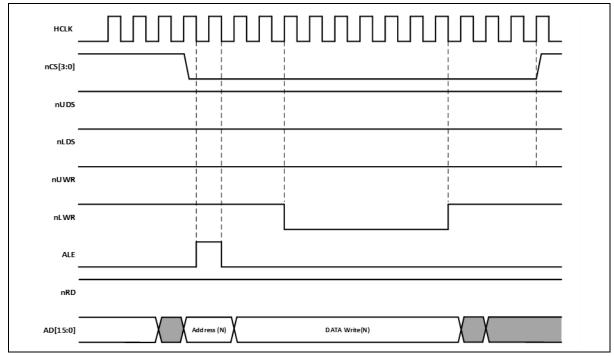

| Figure 55. | Half Word Write Operation with 8-bit Memory and 8-bit Bus               | . 147 |

| Figure 56. | Word Write Operation with 8-bit Memory and 16-bit Bus                   | . 148 |

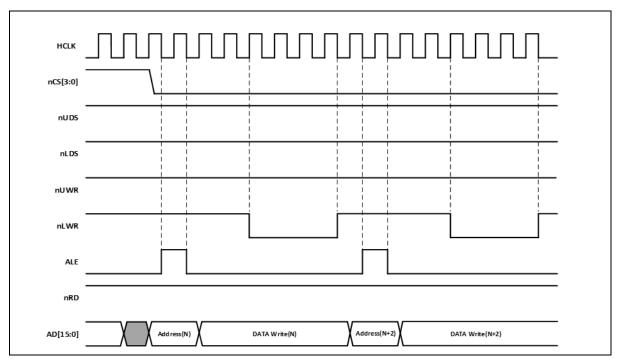

| Figure 57. | Half Word Write Operation with 8-bit Memory and 16-bit Bus              | . 148 |

| Figure 58. | Word Write Operation with 16-bit Memory and 16-bit Bus                  | . 149 |

|            | Half Word Write Operation with 16-bit Memory and 16-bit Bus             |       |

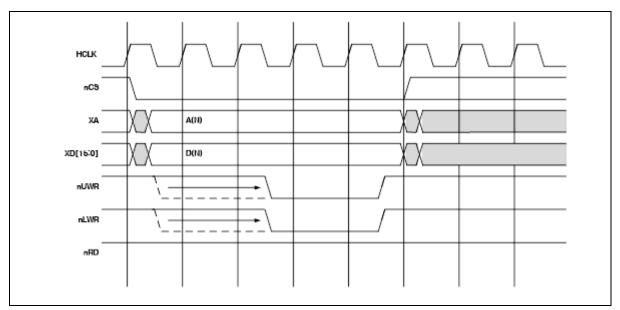

|            | Read Timing Changing by IDLE = 1'                                       |       |

|            | Write Timing Changing by 'PREIDL = 1'                                   |       |

|            | Write Operation with External Wait (nWAIT), 'EXP = 0'                   |       |

|            | WDT Block Diagram                                                       |       |

| -          | WDT Interrupt and WDT Reset Timing Diagram                              |       |

| •          | Watch Timer Block Diagram                                               |       |

|            | 16-bit Timer Block Diagram                                              |       |

|            | TIMER 1n Block Diagram in Timer/Counter Mode (n = 0, 1, 2, and 3)       |       |

|            | Timer/Counter Mode Timing Example of TIMER 1n (n = 0, 1, 2, and 3)      |       |

| -          | Timer/Counter Mode Operation Sequence of TIMER 1n (n = 0, 1, 2, and 3)  |       |

| •          | TIMER 1n Block Diagram in Capture Mode ( $n = 0, 1, 2, and 3$ )         |       |

| -          | Capture Mode Timing Example of TIMER 1n ( $n = 0, 1, 2, and 3$ )        |       |

| -          | Express Timer Overflow in Capture Mode of TIMER 1n (n = 0, 1, 2, and 3) |       |

| -          | Capture Mode Operation Sequence of TIMER 1n ( $n = 0, 1, 2, and 3$ )    |       |

| -          | TIMER 1n Block Diagram in PPG Mode ( $n = 0, 1, 2, and 3$ )             |       |

| -          | PPG Mode Timing Example of TIMER 1n (n = 0, 1, 2, and 3)                |       |

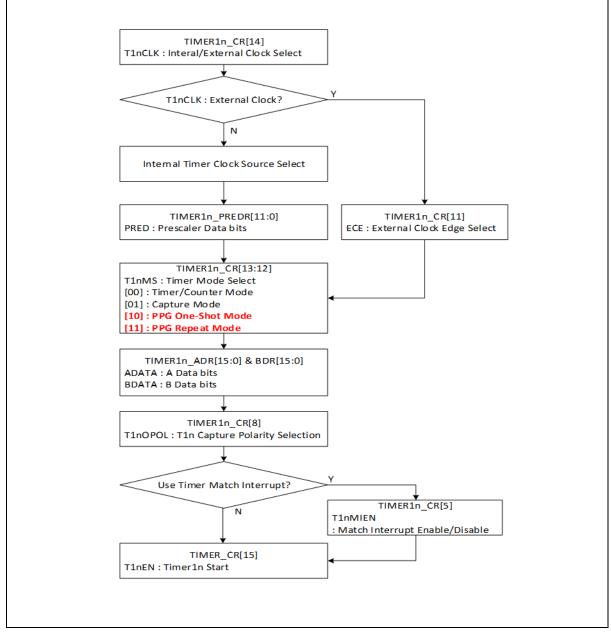

| -          | PPG Mode Operation Sequence of TIMER 1n (n = 0, 1, 2, and 3)            |       |

| -          | 16-bit Timer Block Diagram                                              |       |

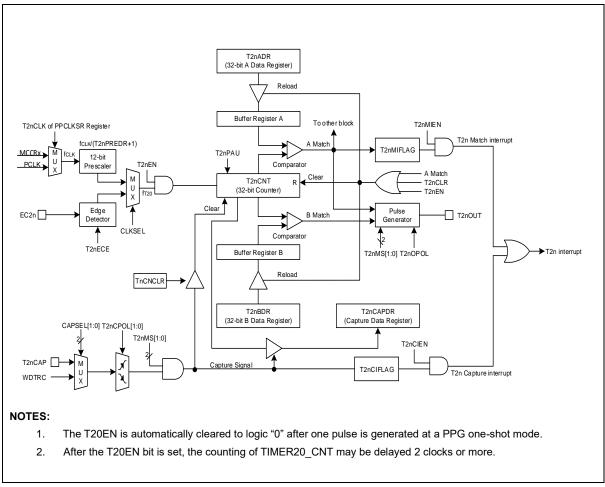

| -          | TIMER 2n Block Diagram in Timer/Counter Mode                            |       |

|            | Timer/Counter Mode Timing Example of TIMER 2n                           |       |

| -          | Timer/Counter Mode Operation Sequence of TIMER 2n (n = 0 or 1)          |       |

| 0          | TIMER 2n Block Diagram in Capture Mode                                  |       |

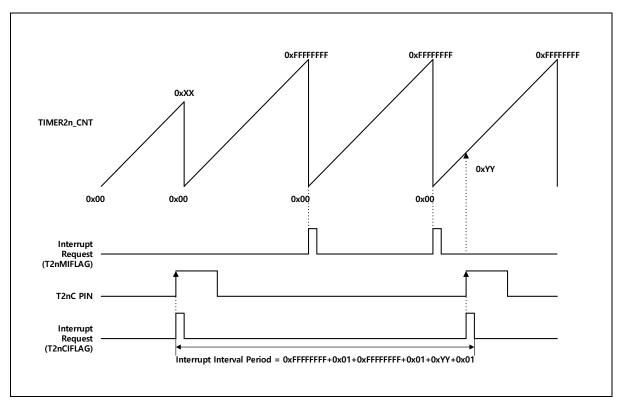

| -          | Capture Mode Timing Example of TIMER 2n (n = 0 and 1)                   |       |

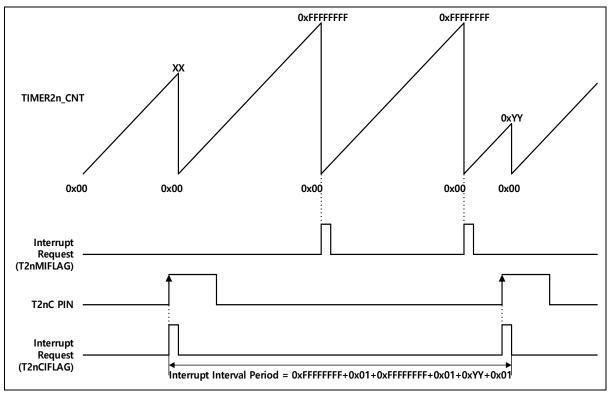

| -          | Express Timer Overflow in Capture Mode of TIMER 2n (T2nCNCLR = 1'b1)    |       |

|            | Express Timer Overflow in Capture Mode of TIMER 2n (T2nCNCER = 1'b0)    |       |

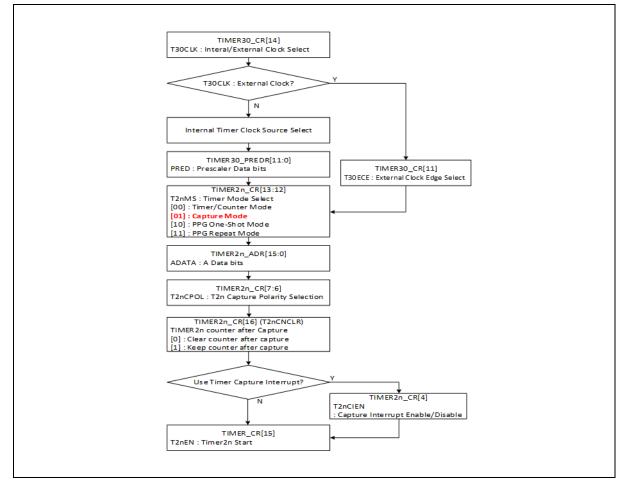

| -          |                                                                         |       |

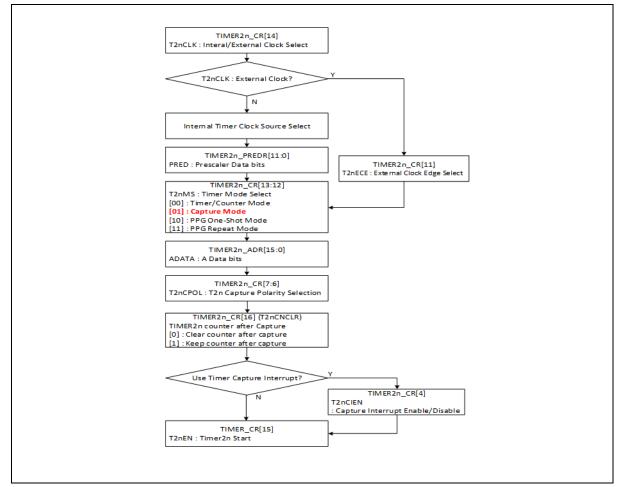

| -          | Capture Mode Operation Sequence of TIMER 2n (n = 0 or 1)                |       |

| -          | TIMER 2n Block Diagram in PPG Mode                                      |       |

| -          | PPG Mode Timing Example of TIMER 2n (n = 0 or 1)                        |       |

| -          | PPG Mode Operation Sequence of TIMER 2n (n = 0 or 1)                    |       |

| •          | Timer Counter 30 Block Diagram                                          |       |

| -          | 16-bit Capture Mode of Timer 30                                         |       |

|            | Capture Mode Operation Sequence of TIMER 30                             |       |

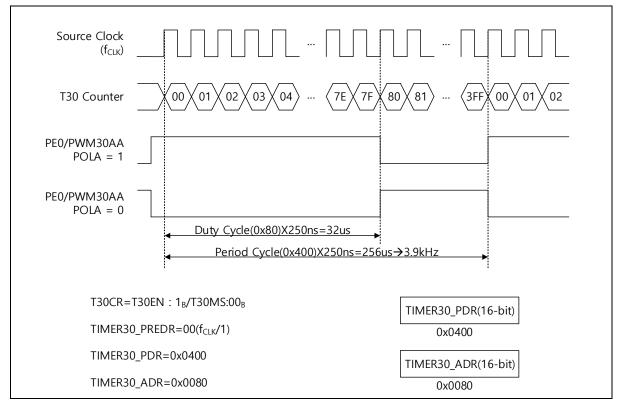

| •          | Example of PWM at 4MHZ                                                  |       |

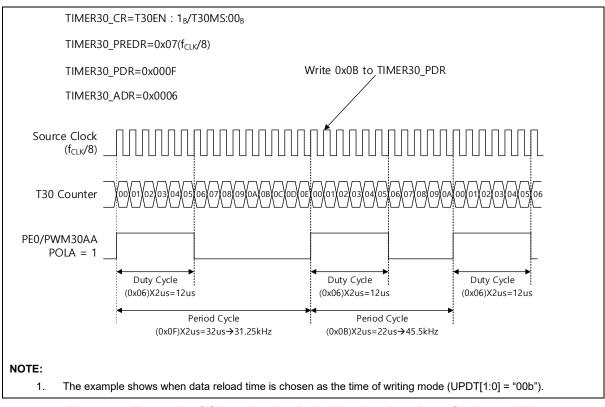

| -          | Example of Changing the Period in Absolute Duty Cycle at 4MHz           |       |

| -          | Interval Mode Timing Chart With "DLYPOS = 0"                            |       |

| -          | Interval Mode Timing Chart With "DLYPOS = 1                             |       |

| -          | Back-to-Back Mode Timing Chart                                          |       |

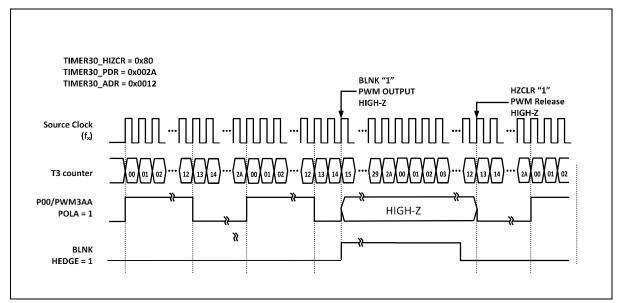

| Figure 97. | Example of PWM External Synchronization with BLNK Input (x: A, B and C) | .218  |

| Figure 00 Everyna of Ferrer A. Chennel Mede                                                | 040   |

|--------------------------------------------------------------------------------------------|-------|

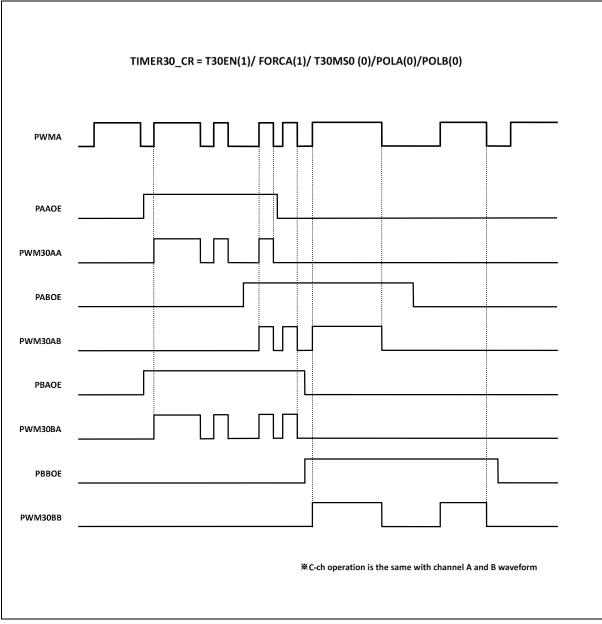

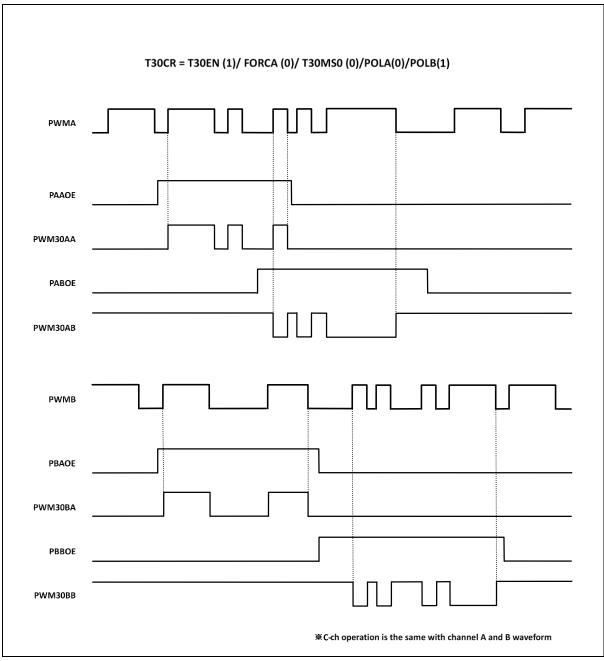

| Figure 98. Example of Force A-Channel Mode                                                 |       |

| Figure 99. Force A-Channel Mode Block Diagram<br>Figure 100. Example of 6-Channel Mode     |       |

| •                                                                                          |       |

| Figure 101. 6-Channel Mode Block Diagram                                                   |       |

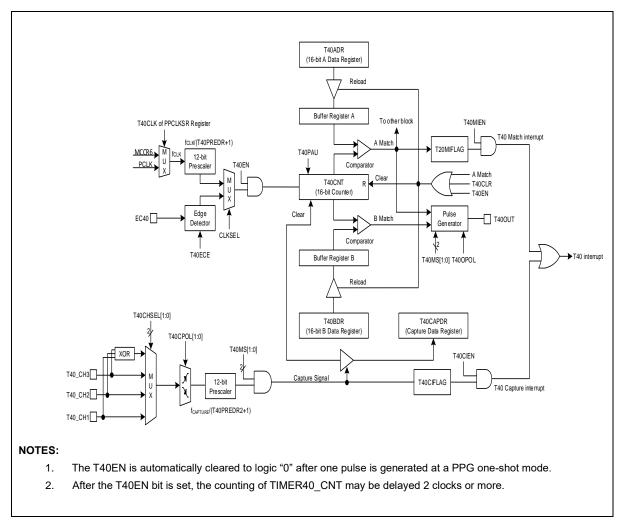

| Figure 102. Timer Counter 40 Block Diagram                                                 |       |

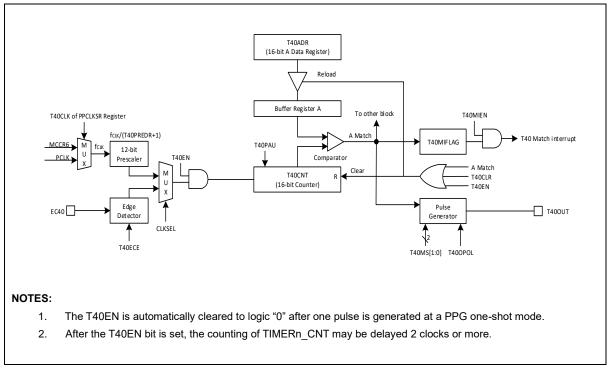

| Figure 103. TIMER 40 Block Diagram in 16-bit Timer/Counter Mode                            |       |

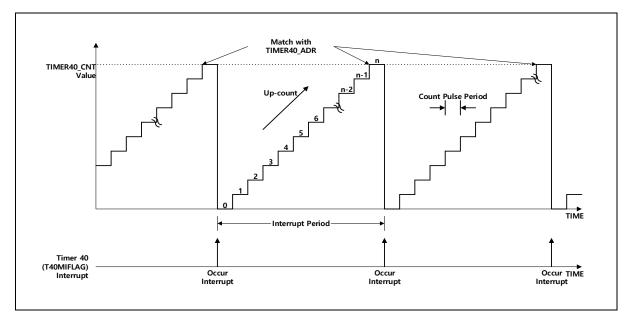

| Figure 104. 16-bit Timer/Counter Mode Timing Example of TIMER 40                           |       |

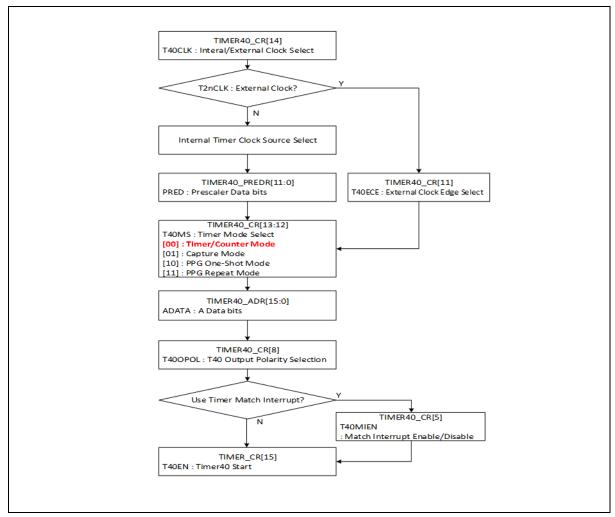

| Figure 105. 16-bit Timer/Counter Mode Operation Sequence of TIMER 40                       |       |

| Figure 106. 16-bit Capture Mode of Timer 40                                                |       |

| Figure 107. Capture Mode Timing Example of TIMER 40                                        |       |

| Figure 108. Express Timer Overflow in Capture Mode of TIMER 40                             |       |

| Figure 109. Capture Mode Operation Sequence of TIMER 40                                    |       |

| Figure 110. TIMER 40 Block Diagram in PPG Mode                                             |       |

| Figure 111. PPG Mode Timing Example of TIMER 40                                            |       |

| Figure 112. PPG Mode Operation Sequence of TIMER 40                                        |       |

| Figure 113. UART Block Diagram (n = 10, 11, 12, and 13)                                    |       |

| Figure 114. SPIN Block Diagram (n = 10, 11, 12, and 13)                                    |       |

| Figure 115. Clock Generation Block Diagram (USARTn, n = 10, 11, 12, and 13)                |       |

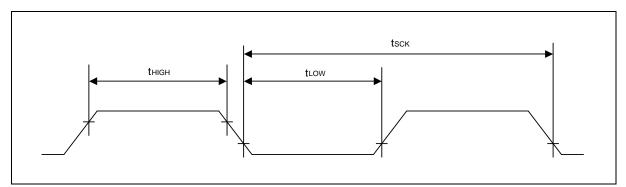

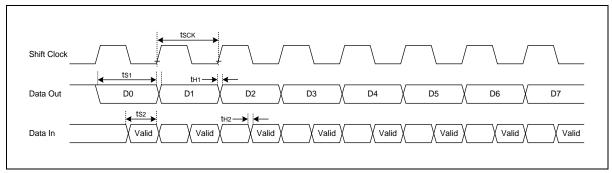

| Figure 116. Synchronous Mode SCKn Timing (USARTn, n = 10, 11, 12, and 13)                  |       |

| Figure 117. Frame Format (USART)                                                           |       |

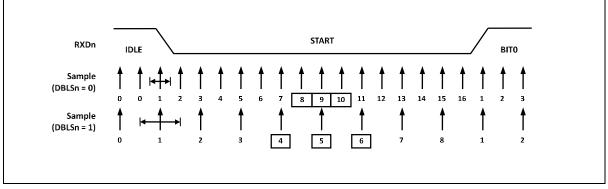

| Figure 118. Asynchronous Start Bit Sampling (n = 10, 11, 12 and 13)                        |       |

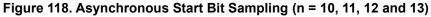

| Figure 119. Asynchronous Data and Parity Bit Sampling (n = 10, 11, 12 and 13)              | 256   |

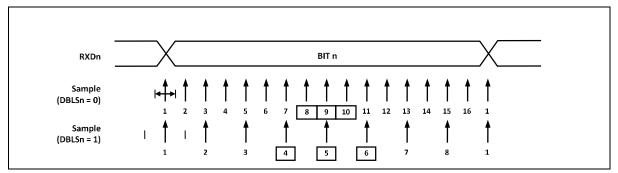

| Figure 120. Stop Bit Sampling and Next Start Bit Sampling (n = 10, 11, 12 and 13)          | 257   |

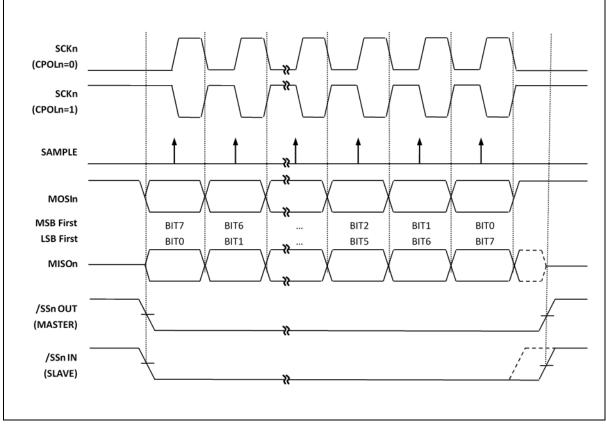

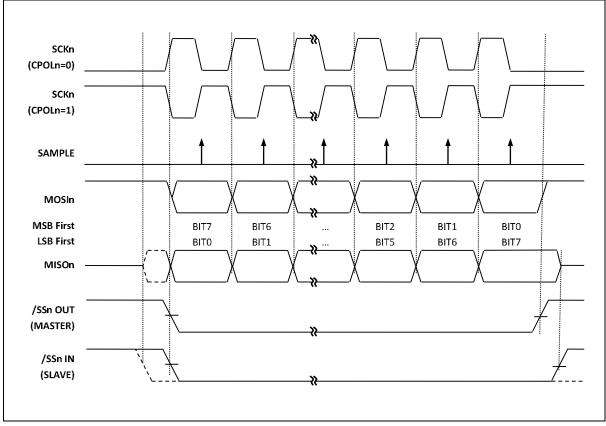

| Figure 121. USART SPIn Clock Formats when CPHAn = 0 (n = 10, 11, 12 and 13)                |       |

| Figure 122. USART SPIn Clock Formats when CPHAn=1 (n = 10, 11, 12 and 13)                  |       |

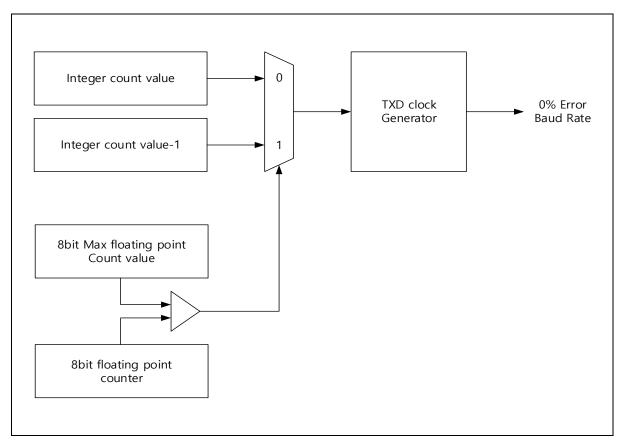

| Figure 123. 0% Error Baud Rate Diagram                                                     |       |

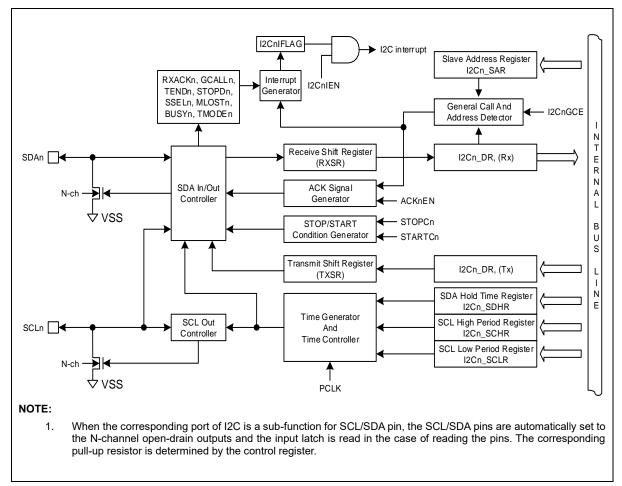

| Figure 124. I2C Block Diagram                                                              | 263   |

| Figure 125. I2C Bus Bit Transfer (n = 0 and 1)                                             | 270   |

| Figure 126. START and STOP Condition (n = 0 and 1)                                         |       |

| Figure 127. I2C Bus Data Transfer (n = 0 and 1)                                            | 271   |

| Figure 128. I2C Bus Acknowledge (n = 0 and 1)                                              | 272   |

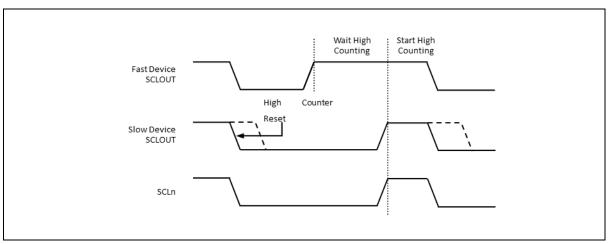

| Figure 129. Clock Synchronization during the Arbitration Procedure (n = 0 and 1)           | 272   |

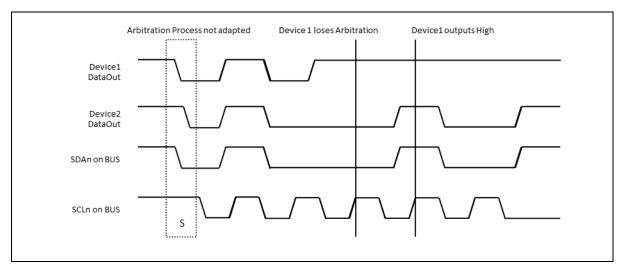

| Figure 130. Arbitration Procedure between Two Masters (n = 0 and 1)                        | 273   |

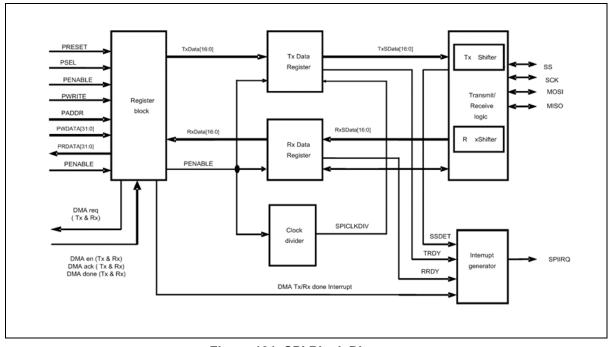

| Figure 131. SPI Block Diagram                                                              | 281   |

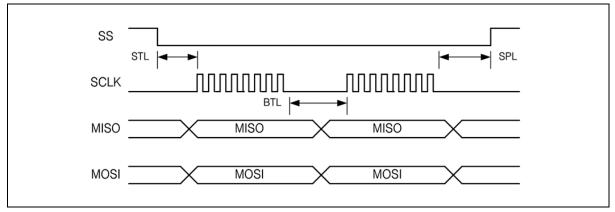

| Figure 132. SPI wave form (STL, BTL and SPL)                                               | 287   |

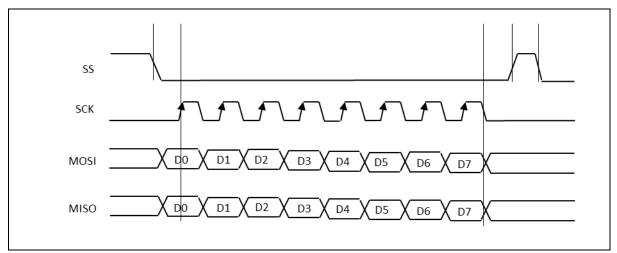

| Figure 133. SPI Transfer Timing 1/4 (CPHA=0, CPOL=0, MSBF=0)                               | 288   |

| Figure 134. SPI Transfer Timing 2/4 (CPHA=0, CPOL=1, MSBF=1)                               | 288   |

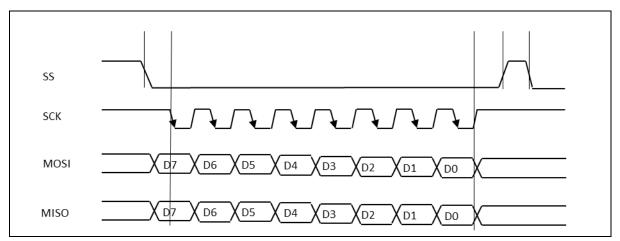

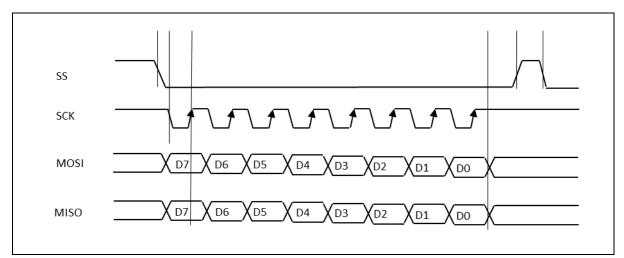

| Figure 135. SPI Transfer Timing 3/4 (CPHA=1, CPOL=0, MSBF=0)                               | 289   |

| Figure 136. SPI Transfer Timing 4/4 (CPHA=1, CPOL=1, MSBF=1)                               | 289   |

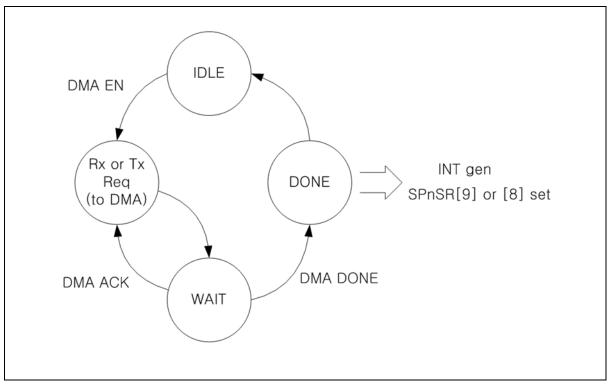

| Figure 137. DMA Handshake Flow Chart                                                       | 290   |

| Figure 138. 12-bit ADC Block Diagram                                                       | 292   |

| Figure 139. ADC Single Mode Timing (When ADC.MR.AMOD = '0')                                | 304   |

| Figure 140. ADC Burst Mode Timing (When ADC.MR.AMOD = '1')                                 | 305   |

| Figure 141. ADC Trigger Timing in Burst Mode (SEQCNT = 3'b111, 8 Sequential Conversion)    |       |

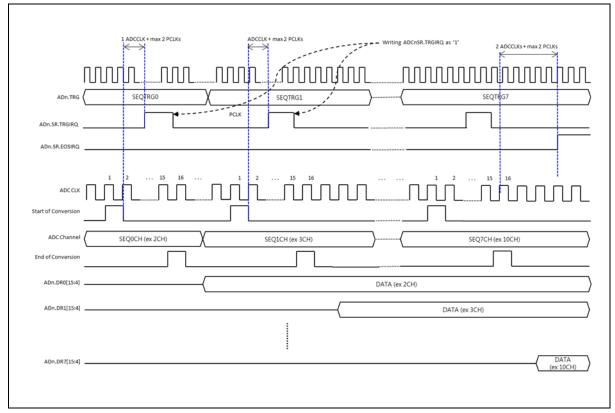

| Figure 142. ADC Sequential Mode Timing (When MR.AMOD = '0' and MR.SEQCNT ≠ '0')            |       |

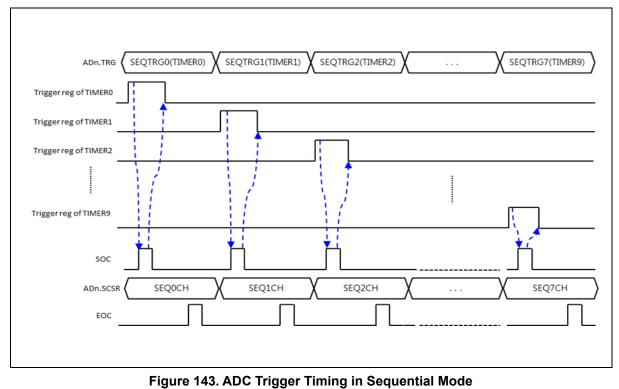

| Figure 143. ADC Trigger Timing in Sequential Mode (SEQCNT = 3'b111, 8 Sequential Conversio | n)306 |

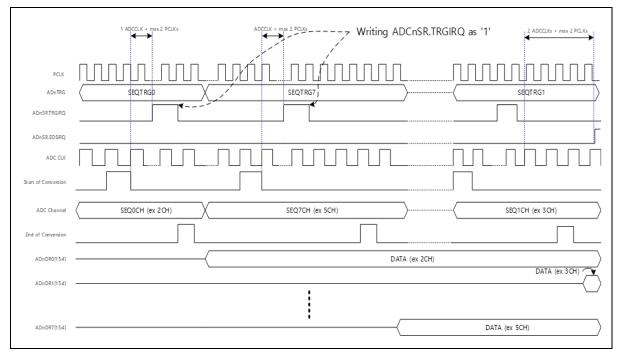

| Figure 144. ADC Multiple Mode Timing (When MR.AMOD = '2' and MR.SEQCNT ≠ '0')              | -     |

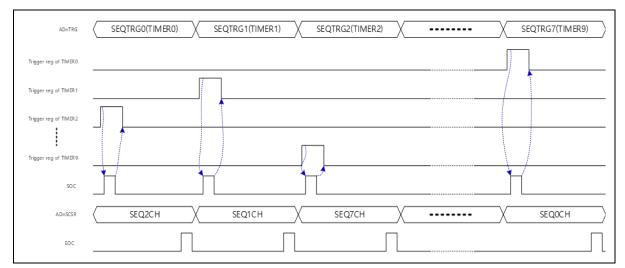

| Figure 145. ADC Trigger Timing in Multiple Mode (SEQCNT = 3'b111, 8 Multiple Conversion)   |       |

| Figure 146. 10-bit DAC Block Diagram                                                       |       |

| Figure 147. Analog Power (AVREF) Pin with a Capacitor                                      |       |

|                                                                                            |       |

| Figure 148.  | DACBR[15:0] Value by a Selected Gain                    | 315 |

|--------------|---------------------------------------------------------|-----|

| Figure 149.  | Comparator Block Diagram                                | 316 |

| Figure 150.  | CRC and Checksum Block Diagram                          | 323 |

| Figure 151.  | CRC Polynomial Structure                                | 327 |

| Figure 152.  | USB Interface Block Diagram                             | 328 |

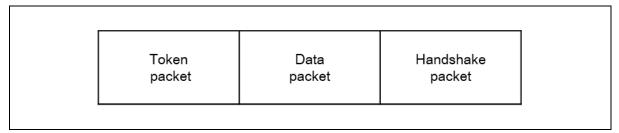

| Figure 153.  | USB Packet Field                                        | 404 |

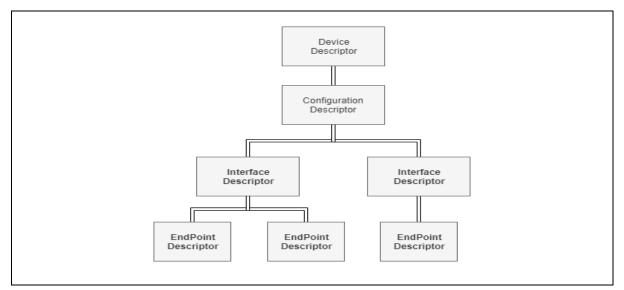

| Figure 154.  | USB Descriptor Hierarchy                                | 405 |

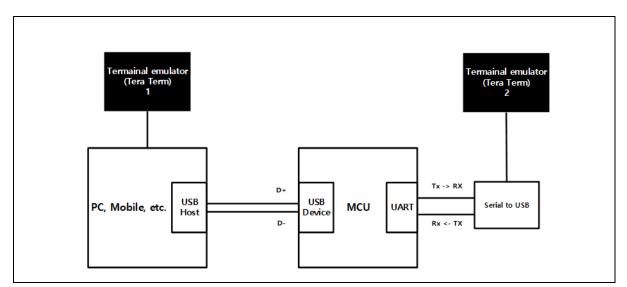

| Figure 155.  | USB Communication using Software                        | 409 |

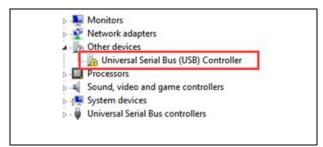

| Figure 156 A | Application Example: Open Windows OS                    | 410 |

| -            | Application Example: Check COM Port                     |     |

| Figure 158.  | Application Example: Printing Characters                | 410 |

|              | HID Block Diagram                                       |     |

| Figure 160.  | USB HID PIPE Example GUI                                | 411 |

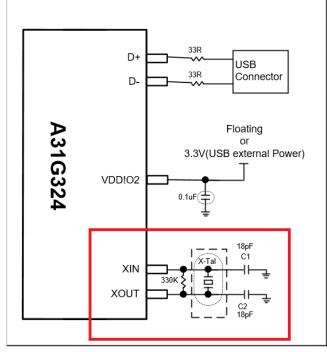

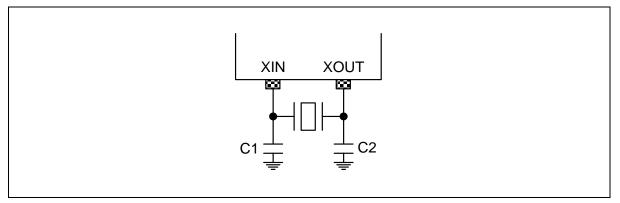

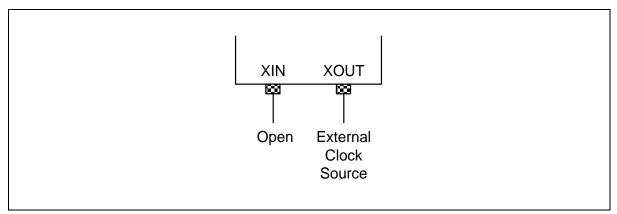

| Figure 161.  | Crystal Design Guide                                    | 412 |

| -            | RTC Block Diagram                                       |     |

| -            | Start Operation Sequence of RTC                         |     |

| Figure 164.  | Read Operation Sequence of RTC                          | 429 |

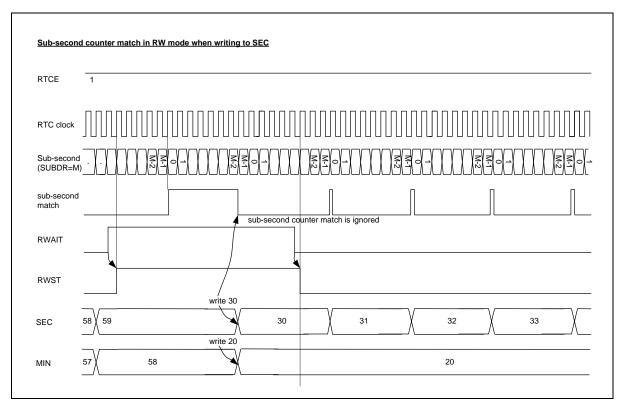

| Figure 165.  | Sub-second Counter Match in RW Mode                     | 430 |

| Figure 166.  | Sub-second Counter Match in RW Mode when Writing to SEC | 430 |

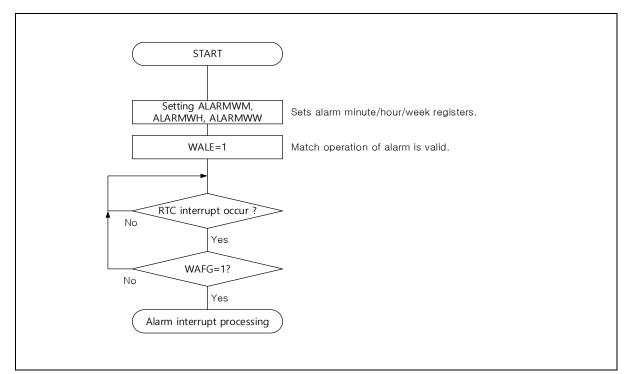

| Figure 167.  | Alarm Operation Sequence of RTC                         | 431 |

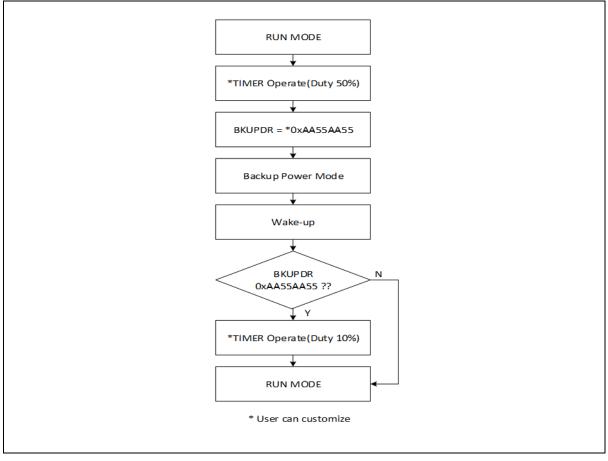

| Figure 168.  | Configuring Sequence of BKUPDR Register                 | 435 |

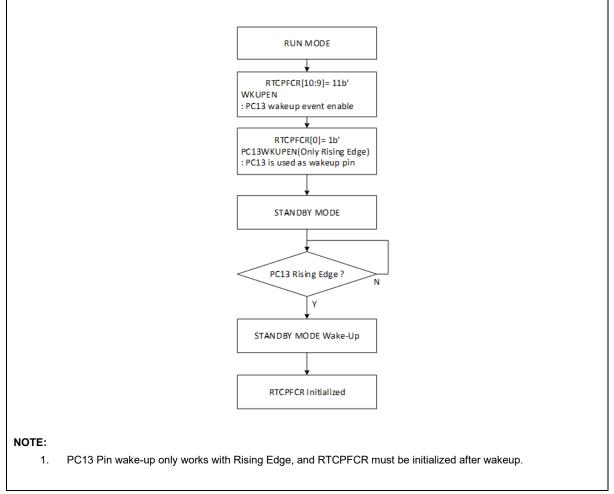

| Figure 169.  | PC13 wakeup in Standby Mode                             | 436 |

| Figure 170.  | Temp Sensor Block Diagram                               | 437 |

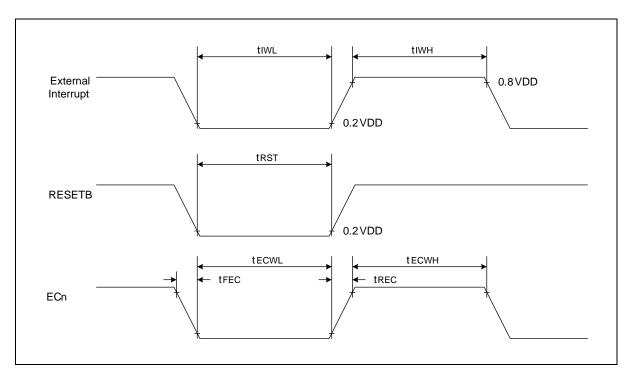

| Figure 171.  | AC Timing                                               | 448 |

| Figure 172.  | SPI Timing                                              | 450 |

| Figure 173.  | I2C Timing                                              | 451 |

| Figure 174.  | Waveform of UART Timing Characteristics                 | 452 |

|              | UART Module Timing                                      |     |

| Figure 176.  | Crystal/Ceramic Oscillator                              | 455 |

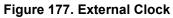

| Figure 177.  | External Clock                                          | 455 |

|              | Clock Timing Measurement at XIN                         |     |

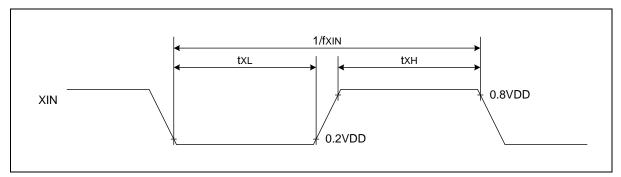

| Figure 179.  | Crystal Oscillator                                      | 456 |

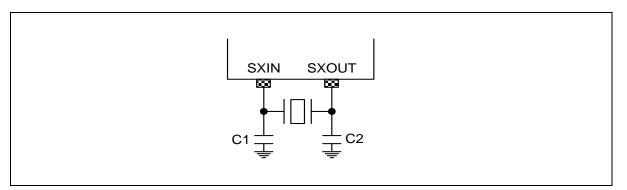

|              | Clock Timing Measurement at SXIN                        |     |

| Figure 181.  | Operating Voltage Range                                 | 457 |

| Figure 182.  | A-Link and Pin Descriptions                             | 461 |

| Figure 183.  | E-PGM+ (Single Writer) and Pin Descriptions             | 462 |

| Figure 184.  | E-Gang4 and E-Gang6 (for Mass Production)               | 462 |

| Figure 185.  | PCB Design Guide for On-Board Programming               | 463 |

| -            | 64 LQFP Package Outline                                 |     |

| Figure 187.  | 48 LQFP Package Outline                                 | 466 |

| Figure 187.  | 48 QFN Package Outline                                  | 468 |

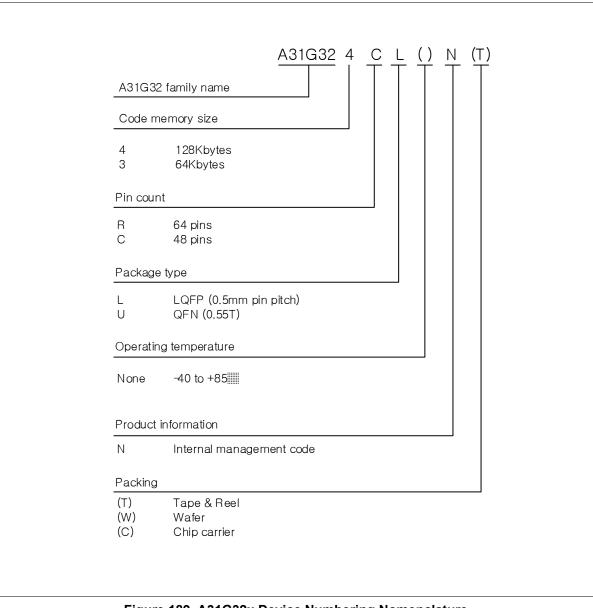

| Figure 188.  | A31G32x Device Numbering Nomenclature                   | 470 |

|              |                                                         |     |

## List of tables

| Table 1. A31G324 and A31G323 Device Features and Peripheral Counts | 19    |

|--------------------------------------------------------------------|-------|

| Table 2. Pin Description                                           |       |

| Table 3. Interrupt Vector Map                                      |       |

| Table 4. A31G32x Memory Boundary Addresses                         |       |

| Table 5. Boot Mode Pin List                                        | 40    |

| Table 6. SCU Pins                                                  | 43    |

| Table 7. Clock Sources                                             | 45    |

| Table 8. Flash Wait Control Recommendation                         | 47    |

| Table 9. Peripheral Clock Select                                   |       |

| Table 10. Reset Sources of Cold Reset and Warm Reset               | 49    |

| Table 11. Operation Mode                                           |       |

| Table 12. Oscillator Control in Power down Mode                    | 56    |

| Table 13. Peripheral Operation in Power down Mode                  | 56    |

| Table 14. STOP Mode Configuration                                  |       |

| Table 15. STANDBY Mode Configuration                               |       |

| Table 16. BACKUP POWER Mode Configuration                          | 61    |

| Table 17. Base Address of SCU (Chip Configuration)                 | 62    |

| Table 18. SCU Register Map (Chip Configuration)                    |       |

| Table 19. Base Address of SCU                                      |       |

| Table 20. SCU Register Map                                         | 63    |

| Table 21. Base Address of LVI/LVR                                  |       |

| Table 22. LVI/LVR Register Map                                     |       |

| Table 23. VDC33 Mode Description                                   |       |

| Table 24. PCU and GPIO pins                                        | . 101 |

| Table 25. GPIO Alternative Function                                | . 103 |

| Table 26. Base Address of PCU                                      |       |

| Table 27. PCU and GPIO Register Map                                |       |

| Table 28. Flash Memory Controller Features                         | . 118 |

| Table 29. Base Address of Flash Memory Controller                  |       |

| Table 30. FMC Register Map                                         |       |

| Table 31. Base Address of DMAC                                     | . 130 |

| Table 32. DMAC Register Map                                        |       |

| Table 33. DMAC PERISEL Selection                                   |       |

| Table 34. Pin Assignment of Static Memory Controller               | . 138 |

| Table 35. Base Address of Static Memory Controller                 | . 139 |

| Table 36. SMIF Register Map                                        | . 139 |

| Table 37. Memory Region Selection and nCS Output by Address        | . 141 |

| Table 38. Data Sort for 8-bit Memory Bus                           | . 141 |

| Table 39. Data Sort for 16-bit Memory Bus                          |       |

| Table 40. Config Signal by A[0]                                    |       |

| Table 41. Base Address of WDT                                      | . 153 |

| Table 42. WDT Register Map                                         | . 153 |

| Table 43. Pre-scaled WDT Counter Clock Frequency                   |       |

| Table 44. Base Address of WT                                       | . 160 |

| Table 45. WT Register Map                                          | . 160 |

| Table 46. Pin Assignment of 16-bit Timer: External Pins            | . 163 |

| Table 47. Base Address of 16-bit Timer                             | . 164 |

| Table 48. TIMER 1n Register Map                                    | . 165 |

| Table 49. | TIMER 1n Operating Modes                                    | . 169 |

|-----------|-------------------------------------------------------------|-------|

| Table 50. | Pin Assignment of 32-bit Timer: External Pins               | . 178 |

| Table 51. | Base Address of 32-bit Timer                                | . 180 |

| Table 52. | TIMER 2n Register Map                                       | . 180 |

| Table 53. | TIMER 2n Operating Modes                                    | . 185 |

| Table 54. | Pin Assignment of Timer Counter 30: External Pins           | . 194 |

| Table 55. | Base Address of Timer Counter 30                            | . 196 |

| Table 56. | Timer Counter 30 Register Map                               | . 196 |

|           | Timer 30 Operating Modes                                    |       |

|           | PWM Channel Polarity                                        |       |

| Table 59. | Pin Assignment of Timer Counter 40: External Pins           | .223  |

| Table 60. | Base Address of Timer Counter 40                            | .225  |

| Table 61. | Timer Counter 30 Register Map                               | .225  |

|           | Timer 40 Operating Modes                                    |       |

|           | Pin Assignment of USART: External Pins                      |       |

|           | Base Address of USART                                       |       |

| Table 65. | USART Register Map                                          | .242  |

|           | Equations for Calculating USART Baud Rate Register Settings |       |

|           | CPOL Functionality                                          |       |

|           | Baud Rate Settings Example                                  |       |

|           | Pin Assignment of I2C: External Pins                        |       |

|           | Base Address of I2C Interface.                              |       |

|           | I2C Register Map                                            |       |

|           | Pin Assignment of SPI: External Pins                        |       |

|           | Base Address of SPI                                         |       |

|           | SPI Register Map                                            |       |

|           | Pin Assignment of ADC: External Signal                      |       |

|           | Base Address of 12-bit ADC                                  |       |

|           | 12-bit ADC Register Map                                     |       |

|           | Trigger Source of ADC                                       |       |

|           | Base Address of DAC                                         |       |

|           | 10-bit DAC Register Map                                     |       |

|           | Base Address of Comparator                                  |       |

|           | Comparator Register Map                                     |       |

|           | Base Address of CRC                                         |       |

|           | CRC Register Map                                            |       |

|           | Base Address of USB Interface                               |       |

|           | USB Interface Register Map                                  |       |

|           | USB Packet PID                                              |       |

|           | Base Address of RTC Interface                               |       |

|           | RTC Register Map                                            |       |

|           | Specified time system by AMPM                               |       |

|           | SUBDR and RTC Clock Combination for 1Hz.                    |       |

|           | WEEK and ALARMWW Registers                                  |       |

|           | Example of Setting the Alarm                                |       |

|           | Correction Resolution by Frequency                          |       |

|           | PC13, PC14, PC15 Function in RTCPFCR register               |       |

|           | Base Address of TSENSE Interface                            |       |

|           | TSENSE Register Map                                         |       |

|           | Specific temperature value in the region of OTP             |       |

| 10010 30. |                                                             | . ++0 |

| Table 99. A | Absolute maximum rating                                       | 441 |

|-------------|---------------------------------------------------------------|-----|

| Table 100.  | Recommended Operating Condition                               | 442 |

| Table 101.  | ADC Electrical Characteristics                                | 442 |

| Table 102.  | DAC Electrical Characteristics                                | 443 |

|             | POR Electrical Characteristics                                |     |

| Table 104.  | Low Voltage Reset/Indicator Characteristics                   | 444 |

| Table 105.  | High Frequency Internal RC Oscillator Characteristics         | 445 |

| Table 106.  | Low Frequency (750KHz) Internal RC Oscillator Characteristics | 445 |

| Table 107.  | Low Frequency (40KHz) Internal RC Oscillator Characteristics  | 445 |

|             | DC Electrical Characteristics                                 |     |

| Table 109.  | Supply Current Characteristics                                | 447 |

| Table 110.  | AC Characteristics                                            | 448 |

| Table 111.  | SPI Characteristics with High Voltage                         | 449 |

| Table 112.  | SPI Characteristics with Low Voltage                          | 449 |

|             | I2C Characteristics                                           |     |

| Table 114.  | UART Timing Characteristics                                   | 452 |

| Table 115.  | Data Retention Voltage in STOP mode                           | 453 |

| Table 116.  | Internal Flash ROM Characteristics                            | 453 |

| Table 117.  | Main Oscillator Characteristics                               | 454 |

| Table 118.  | Sub Oscillator Characteristics                                | 456 |

| Table 119.  | PLL Electrical Characteristics                                | 457 |