4-BIT SINGLE CHIP MICROCOMPUTERS

# ADAM46P20XX USER'S MANUAL

- ADAM46P2016

- ADAM46P2016T

- ADAM46P2014

- ADAM46P2014D

- ADAM46P2010

- ADAM46P2008

- ADAM46P2008T

- ADAM46P2008D

# 0. Revision History

| Version | Date       | Description                                                                                                                                                                      |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VER 0.0 | 2010.11.17 | 1'st Release.                                                                                                                                                                    |

| VER 0.1 | 2010.12.03 | Change the VDI Level : 3.6V → 3.3V, 2.4V → 2.2V<br>Change the LVD Level : 2.0V → 1.8V, 2.4V → 2.2V<br>Change the Operating Voltage : 2.0V~5.5V @4MHz<br>Correct the some Errata. |

| VER 0.2 | 2010.12.04 | Add the Package types (14-DIP, 10-MSOP, 8-DIP)                                                                                                                                   |

| VER 0.3 | 2011.01.27 | Remove a instruction ( "LPG" ) Change the "S" bit of SFR in reset state.                                                                                                         |

| VER 0.4 | 2011.04.05 | Add the peripheral register ( "ABR3" ).                                                                                                                                          |

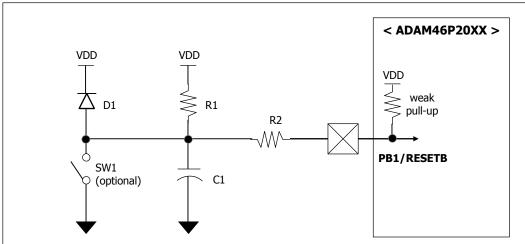

| VER 0.5 | 2011.07.21 | Add the External RESETB Circuit.                                                                                                                                                 |

| VER 1.0 | 2012.07.15 | Change the Operating Voltage Spec (page-2, 15)  Ver 0.5:                                                                                                                         |

| VER 1.1 | 2015.12.3  | Add the chapter `1.7.5 POR Electrical Characteristics'. (19 page) Add the electrical specification of LVD & Temperature characteristics. (16, 18 page)                           |

|         |            |                                                                                                                                                                                  |

|         |            |                                                                                                                                                                                  |

|         |            |                                                                                                                                                                                  |

|         |            |                                                                                                                                                                                  |

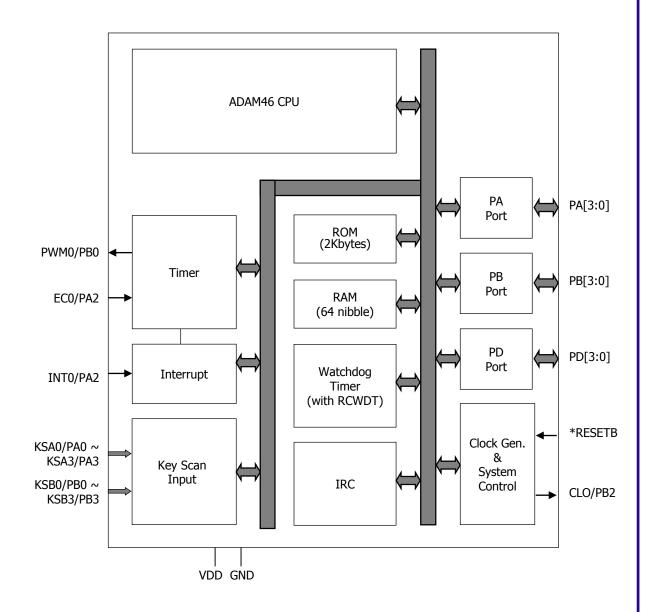

The ADAM46P20XX is the High Speed and Low Voltage operating 4-bit single chip microcomputer. This chip contains ADAM46 CPU, EPROM, RAM, Timer/Count, Interrupt, Watch Dog Timer, Input/Output Ports and Oscillation Circuit.

#### 1.1. Features

- ◆ Instruction Execution Time

- 500ns @ fosc=8MHz

- Program Memory Area (OTP)

- 2K Bytes (1,024 x 16bit)

- ◆ Data memory (RAM)

- 64 nibble (64 x 4bit)

- ▶ 16-Bit Table read Instruction.

- ◆ Timer (Timer/Counter/Capture/PWM)

- 8Bit x 1ch

- ♦ Watch-Dog Timer (with RCWDT=64kHz)

- 19Bit x 1ch

- Oscillator Type

- Calibrated Internal RCOSC: typ. 16/8/4/2/1/0.5MHz selectable

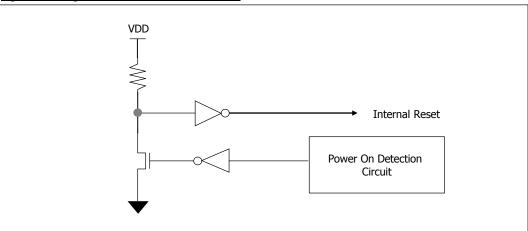

- ◆ Power On Reset

- Power Saving Operation Modes

- STOP

- RCWDT

- Interrupt Sources

- External : 1ch (INT0)

- Internal : 3ch (T0, WDT, VDI)

- ◆ Reset

- Built-in Watch-dog timer

- Built-in Power-on Reset (POR)

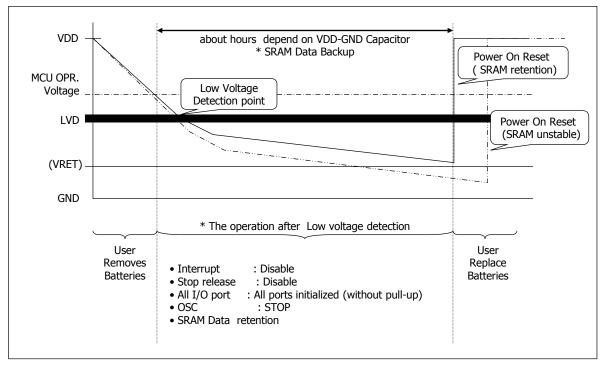

- Built-in Low Voltage Detection & Reset (LVD)

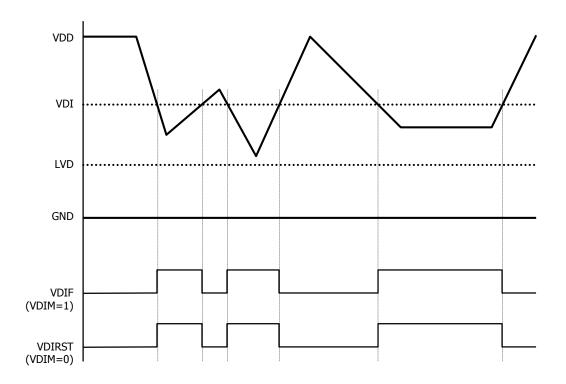

- Built-in Voltage Detection Indicator & Reset (VDI)

- External RESETB

- Low Voltage Detection Reset Circuit

- ◆ 2-level Voltage Detection Indicator (3.3V/2.2V)

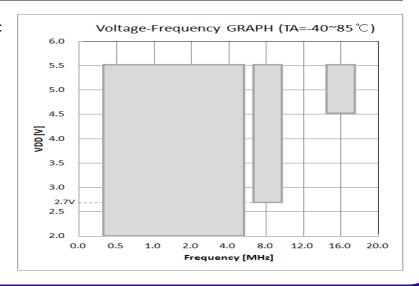

- Operating Voltage Range

- 2.0 ~ 5.5 V @ 0.5MHz ~ 4MHz

- 2.7 ~ 5.5 V @ 8MHz

- 4.5 ~ 5.5 V @ 16MHz

- ◆ Operating Temperature Range

- -40 ~ 85 °C

#### ☑ ADAM46P20XX Device Summary

| Series            | ADAM46P2016  | ADAM46P2014 | ADAM46P2010 | ADAM46P2008     |

|-------------------|--------------|-------------|-------------|-----------------|

| Program<br>memory | 1,024 x 16   | 1,024 x 16  | 1,024 x 16  | 1,024 x 16      |

| Data memory       | 64 x 4       | 64 x 4      | 64 x 4      | 64 x 4          |

| I/O ports         | 12           | 12          | 8           | 6               |

| Package           | 16-SOP/TSSOP | 14-SOP/DIP  | 10-MSOP     | 8-SOP/TSSOP/DIP |

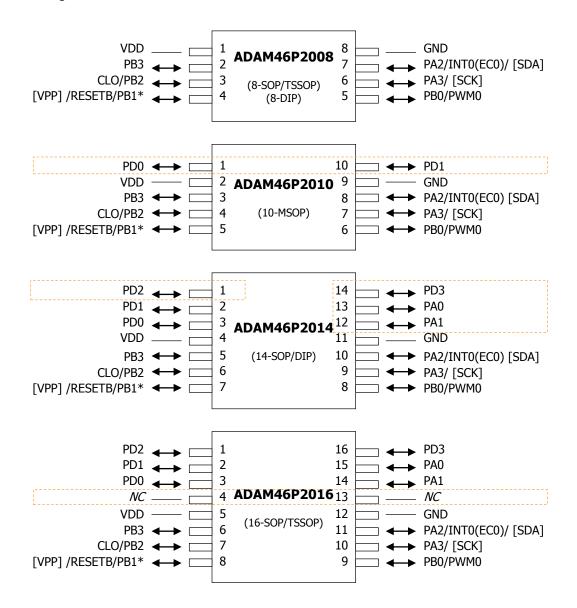

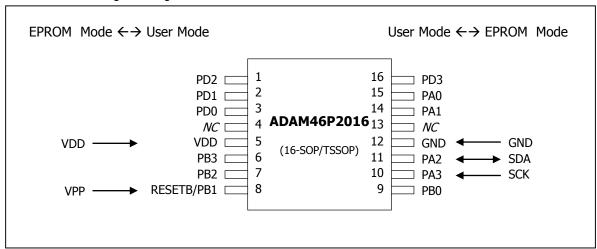

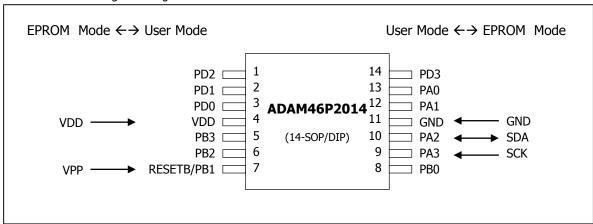

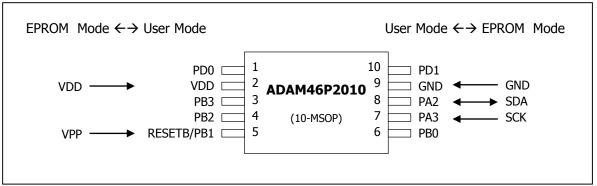

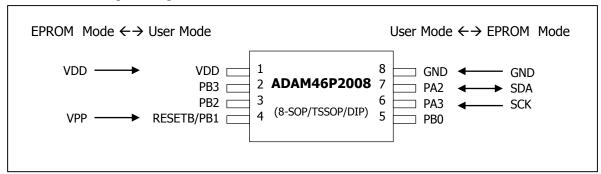

#### 1.2. Pin Assignments

\* RESETB is selected by setting the OTP Configuration Bit.

## 1.3. Block Diagram

\* RESETB is selected by setting the OTP Configuration Bit.

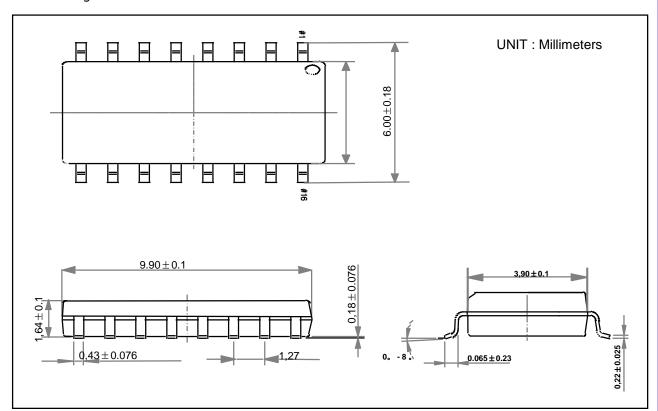

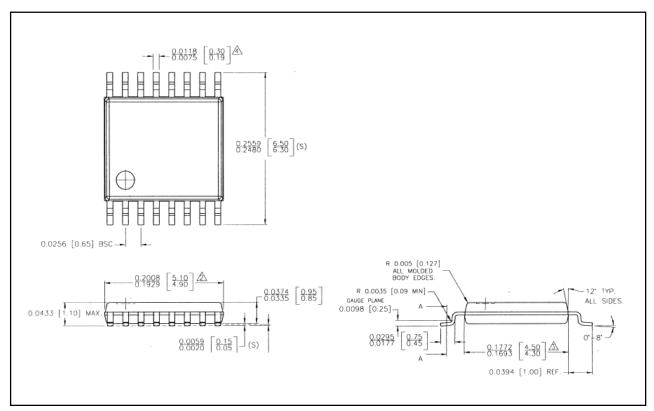

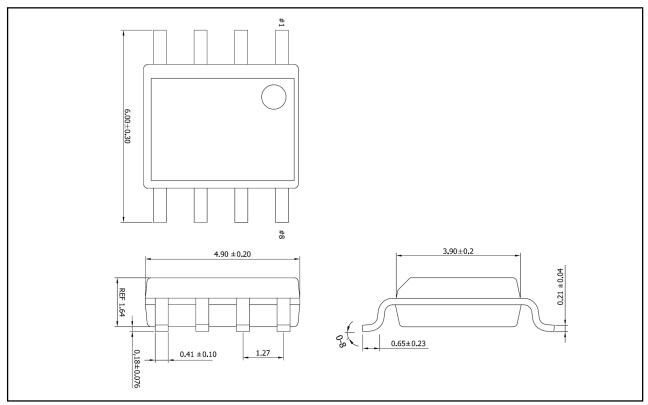

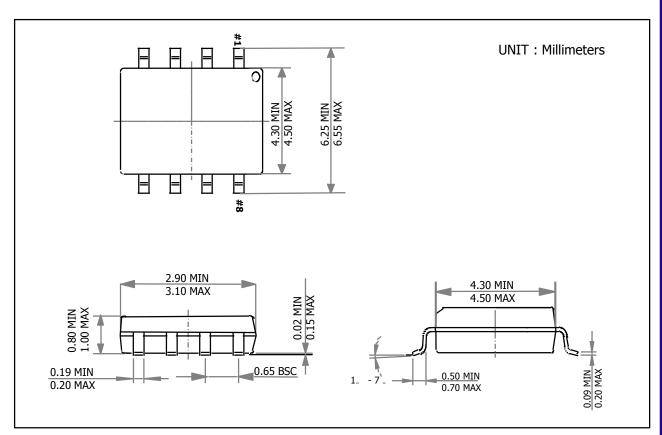

## 1.4. Package Dimension

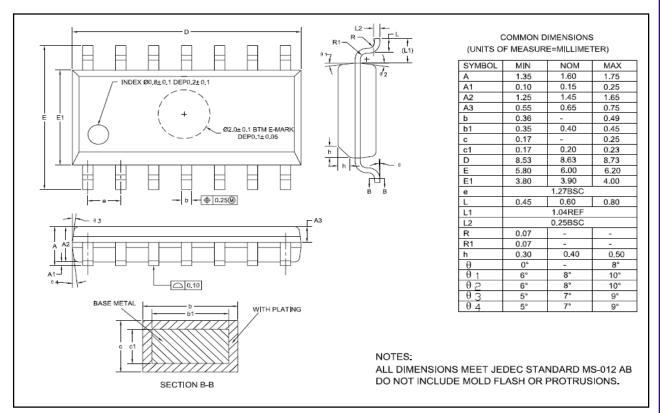

16 SOP (150Mil) Pin Dimension (dimensions in millimeters)

16 TSSOP (4.4 mm) Pin Dimension (dimensions in inch [millimeters])

14 SOP (150Mil) Pin Dimension (dimensions in millimeters)

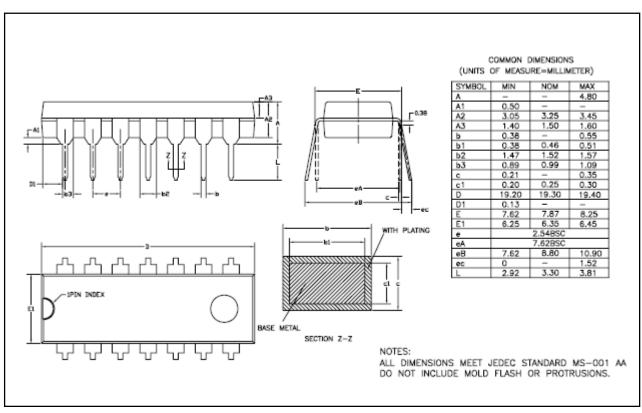

14 DIP (300Mil) Pin Dimension (dimensions in millimeters)

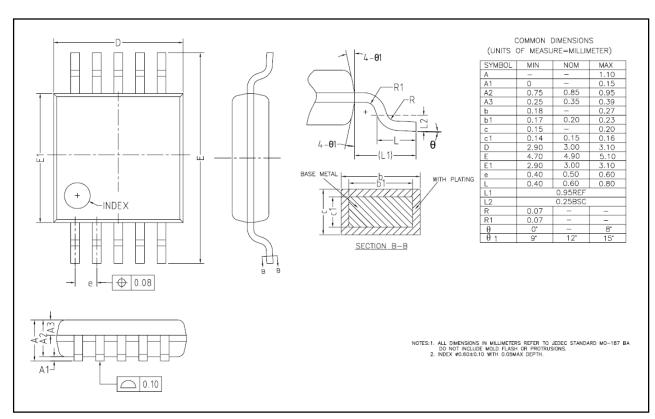

10 MSOP Pin Dimension (dimensions in millimeters)

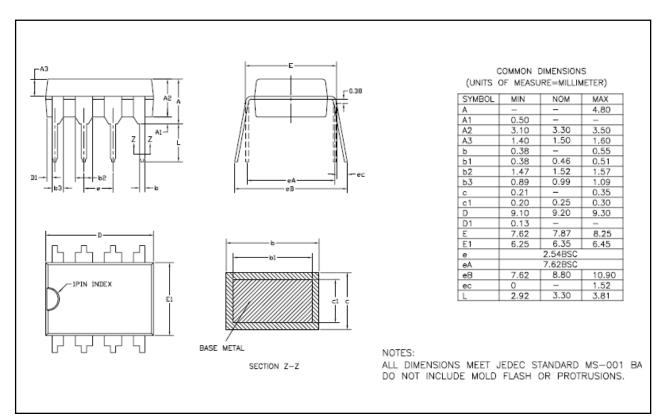

8 DIP (300Mil) Pin Dimension (dimensions in millimeters)

8 SOP (150Mil) Pin Dimension (dimensions in millimeters)

8 TSSOP (4.4 mm) Pin Dimension (dimensions in inch [millimeters])

## 1.5. Pin Function

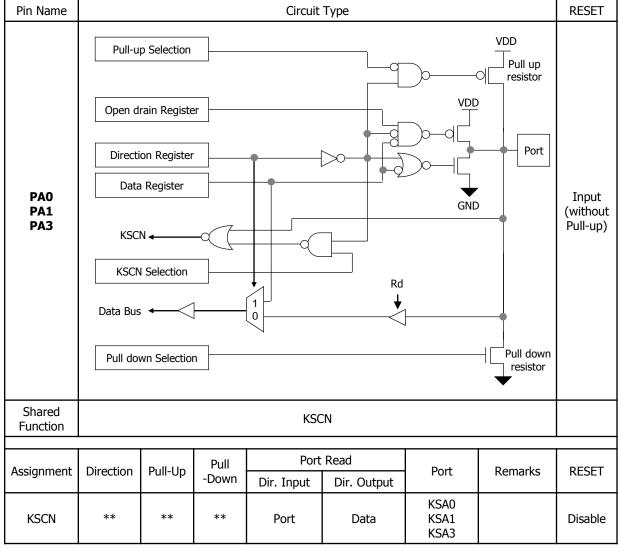

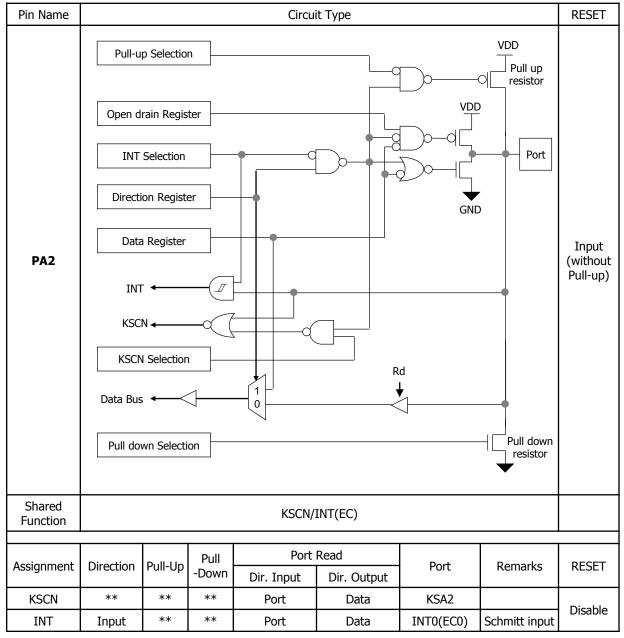

#### 1.5.1. Port Pins

| Pin<br>Name | 1/0 | Function                                                                                                                                                                    | @RESET                        | @STOP                      | Shared<br>Pins |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------|----------------|

| PA0         |     | - 4-bit I/O Port.                                                                                                                                                           |                               |                            | KSA0           |

| PA1         |     | - CMOS input Push-pull output.                                                                                                                                              | Input                         | State                      | KSA1           |

| PA2         | 1/0 | <ul> <li>Each pin can be set and reset by Data register value.</li> <li>Can be programmable as N-ch open drain/Pull-up/<br/>Pull-down/KSCN/INT(EC) individually.</li> </ul> | (without<br>Pull-up)          | of before<br>STOP          | INT0(EC0)/KSA2 |

| PA3         |     | - Direct driving of LED (N-TR).                                                                                                                                             |                               |                            | KSA3           |

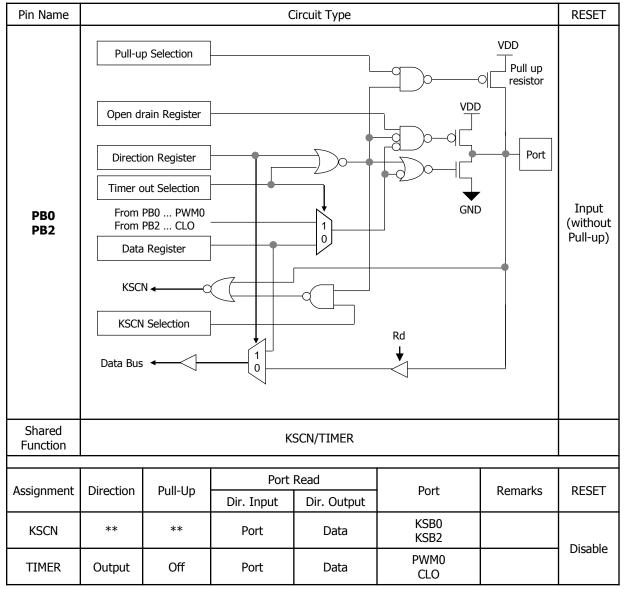

| PB0         |     | - 4-bit I/O Port.<br>- CMOS input.                                                                                                                                          | Input<br>(without<br>Pull–up) | State<br>of before<br>STOP | PWM0/KSB0      |

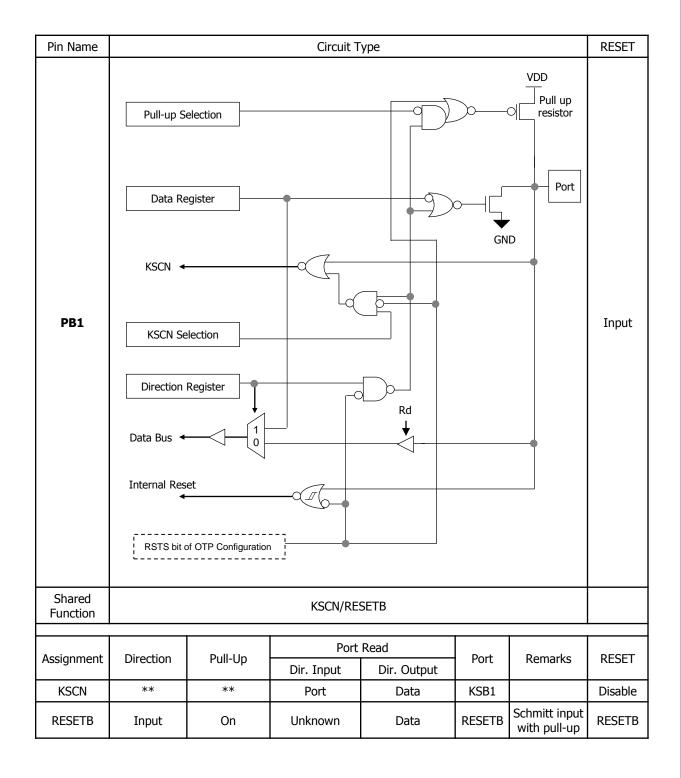

| PB1         | 1/0 | Push-pull output (except PB1).  - Each pin can be set and reset by Data register value.                                                                                     |                               |                            | RESETB/KSB1    |

| PB2         | 1/0 | - Can be programmable as N-ch open drain/Pull-up/<br>KSCN/Clock/TIMER output individually.                                                                                  |                               |                            | CLO/KSB2       |

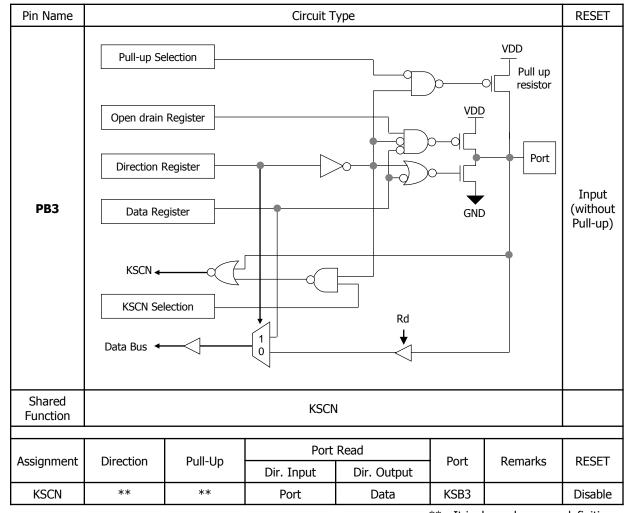

| PB3         |     | - Direct driving of LED (N-TR).<br>- PB1 is N-ch Open drain output only at output mode.                                                                                     |                               |                            | KSB3           |

| PD0         |     | - 4-bit I/O Port.                                                                                                                                                           |                               |                            | -              |

| PD1         | 1/0 | - CMOS input Push-pull output.                                                                                                                                              | Input<br>(without             | State                      | -              |

| PD2         | 1/0 | <ul> <li>Each pin can be set and reset by Data register value.</li> <li>Can be programmable as N-ch open drain/Pull-up/individually.</li> </ul>                             |                               | of before<br>STOP          | _              |

| PD3         |     | - Direct driving of LED (N-TR).                                                                                                                                             |                               |                            | _              |

#### 1.5.2. Non-Port Pins

| Pin<br>Name | I/O | Function                                                                                                                                              | @RESET              | Shared<br>Pins |

|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|

| INTO        | I   | - External Interrupt input for which the valid edges (rising edge, falling edge, both rising and falling edge) can be specified Timer0 capture input. | Input (Pull-up off) | PA2            |

| EC0         | I   | - Timer0 event counter input.                                                                                                                         | Input (Pull-up off) | PA2            |

| PWM0        | 0   | - 8-bit PWM0 (shared with Timer0) output.                                                                                                             | Input (Pull-up off) | PB0            |

| CLO         | 0   | - System Clock output. (Fosc)                                                                                                                         | Input (Pull-up off) | PB2            |

| KSA0 ~ KSA3 |     | - STOP mode release input which can be selected                                                                                                       |                     | PA0 ~ PA3      |

| KSB0 ~ KSB3 | ı   | individually by user program.<br>- It is released by "L" input at STOP mode.                                                                          | Input (Pull-up off) | PB0 ~ PB3      |

| RESETB      | ı   | - External RESETB Input by Code Option.                                                                                                               | Input (Pull-up off) | PB1            |

| VDD         | Р   | - Positive power supply.                                                                                                                              | _                   | _              |

| GND         | Р   | - Ground.                                                                                                                                             | _                   | _              |

# 1.5.3. OTP Programming Pin Description (OTP Program Mode)

|      | Pin   | No.   |       | Dia Nama | 1/0 | Fire extinu                                      | Oharad Bira   |

|------|-------|-------|-------|----------|-----|--------------------------------------------------|---------------|

| 8Pin | 10pin | 14pin | 16pin | Pin Name | 1/0 | Function                                         | Shared Pins   |

| #1   | #2    | #4    | #5    | VDD      | Р   | - Programming Power supply (+ 5.0V)              | VDD           |

| #4   | #5    | #7    | #8    | VPP      | Р   | - Programming high voltage Power supply (+11.5V) | PB1/RESETB    |

| #8   | #9    | #11   | #12   | GND      | Р   | - Ground                                         | GND           |

| #6   | #7    | #9    | #10   | SCK      | 1   | - Programming Clock input pin                    | PA3           |

| #7   | #8    | #10   | #11   | SDA      | 1/0 | - Programming Data Input/Output pin              | PA2/INT0(EC0) |

#### 1.6. Port Structure

<sup>\*\*:</sup> It is depend on user definition.

\*\* : It is depend on user definition.

<sup>\*\*:</sup> It is depend on user definition.

\*\*: It is depend on user definition.

\*\*: It is depend on user definition.

| Pin Name                 | Circuit Type                                                                                                  | RESET                         |

|--------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------|

| PD0<br>PD1<br>PD2<br>PD3 | Pull-up Selection  Pull up resistor  Open drain Register  Direction Register  Data Register  Rd  GND  Rd  GND | Input<br>(without<br>Pull-up) |

| Shared<br>Function       |                                                                                                               |                               |

#### 1.7. Electrical Characteristics

#### 1.7.1. Absolute Maximum Ratings (Ta = 25°C)

| PARAMETER           | SYMBOL           | RATINGS          | UNIT |

|---------------------|------------------|------------------|------|

| Supply Voltage      | $V_{DD}$         | -0.3 ~ +6.0      | V    |

| Input Voltage       | $V_{\mathrm{I}}$ | -0.3 ~ VDD + 0.3 | V    |

| Output Voltage      | Vo               | -0.3 ~ VDD + 0.3 | V    |

| Storage Temperature | T <sub>STG</sub> | -65 ~ 150        | οС   |

| Power Dissipation   | $P_{D}$          | 700              | mW   |

# 1.7.2. Recommended Operating Ranges

| PARAMETER             | SYMBOL           | CONDITION                                 | MIN.  | TYP.  | MAX   | UNIT |

|-----------------------|------------------|-------------------------------------------|-------|-------|-------|------|

|                       |                  | $f_{OSC} = 0.5M \sim 4MHz$                | 2.0   | -     | 5.5   | V    |

| Supply Voltage        | $V_{DD}$         | $f_{OSC} = 8MHz$                          | 2.7   | -     | 5.5   | ٧    |

|                       |                  | f <sub>OSC</sub> = 16MHz                  | 4.5   | -     | 5.5   | V    |

| Operating Temperature | T <sub>OPR</sub> |                                           | -40   | -     | 85    | °C   |

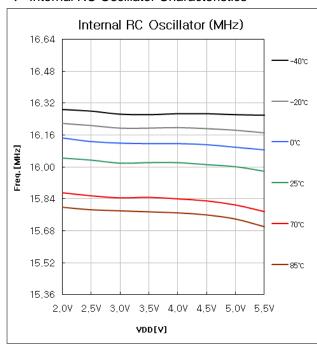

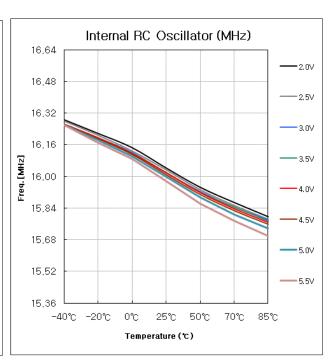

|                       |                  |                                           | 15.68 | 16.00 | 16.32 |      |

|                       |                  |                                           | 7.84  | 8.00  | 8.16  |      |

|                       |                  | Calibrated                                | 3.92  | 4.00  | 4.08  | MHz  |

|                       |                  | Internal RC Oscillator<br>(Ta=-20 ~ 70°C) | 1.96  | 2.00  | 2.04  |      |

|                       |                  |                                           | 0.98  | 1.00  | 1.02  |      |

|                       |                  |                                           | 0.490 | 0.500 | 0.510 |      |

| Oscillation Fraguency | £                |                                           | (-2%) | -     | (+2%) |      |

| Oscillation Frequency | f <sub>osc</sub> |                                           | 15.52 | 16.00 | 16.48 |      |

|                       |                  |                                           | 7.76  | 8.00  | 8.24  |      |

|                       |                  | Calibrated                                | 3.88  | 4.00  | 4.12  |      |

|                       |                  | Internal RC Oscillator                    | 1.94  | 2.00  | 2.06  |      |

|                       |                  | (Ta=-40~85°C)                             | 0.97  | 1.00  | 1.03  |      |

|                       |                  |                                           | 0.485 | 0.500 | 0.515 |      |

|                       |                  |                                           | (-3%) | -     | (+3%) |      |

# ► Voltage-Frequency Graph :

#### 1.7.3. DC Characteristics (Ta = $25^{\circ}$ C)

| 1.7.3. DC Charac                      | teristics          | (1a = 25 C)                                                                                |           |                                                       | 1       |      |                                                  |            |

|---------------------------------------|--------------------|--------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------|---------|------|--------------------------------------------------|------------|

| PARAMETER Symbol                      |                    | Condition                                                                                  |           |                                                       | S       | UNIT |                                                  |            |

|                                       | -,                 |                                                                                            |           |                                                       | MIN.    | TYP. | MAX.                                             |            |

| High level                            | V <sub>IH1</sub>   | RESETB, INTO/ECO                                                                           |           |                                                       | 0.8VDD  |      | VDD                                              | V          |

| input voltage                         | V <sub>IH2</sub>   | PA, PB, PD                                                                                 |           |                                                       | 0.7VDD  |      | VDD                                              | V          |

| Low level                             | $V_{IL1}$          | RESETB, INTO/ECO                                                                           |           |                                                       | 0       |      | 0.2VDD                                           | V          |

| input voltage                         | V <sub>IL2</sub>   | PA, PB, PD                                                                                 | 1         |                                                       | 0       |      | 0.3VDD                                           | V          |

| High level input<br>leakage current   | $I_{IH}$           | PA, PB, PD                                                                                 |           | VIH = VDD                                             |         |      | 1                                                | uA         |

| Low level input<br>leakage current    | $I_{IL}$           | PA, PB, PD                                                                                 |           | VIL = 0V                                              |         |      | -1                                               | uA         |

| High level<br>output voltage          | V <sub>OH1</sub>   | PA, PB, PD<br>(Except PB1)                                                                 | VDD = 5V  | IOH = -10mA                                           | VDD-1.0 |      |                                                  | V          |

| Low level<br>output voltage           | V <sub>OL1</sub>   | PA, PB, PD                                                                                 | VDD = 5V  | IOL = 15mA                                            |         |      | 1.0                                              | V          |

| High level output<br>leakage current  | I <sub>OHL</sub>   | PA, PB, PD                                                                                 |           | VOH = VDD                                             |         |      | 1                                                | uA         |

| Low level output<br>leakage current   | I <sub>OLL</sub>   | PA, PB, PD                                                                                 |           | VOL = 0V                                              |         |      | -1                                               | uA         |

| Input Pull-up<br>Current              | $I_{PU}$           | PA, PB, PD                                                                                 | VDD = 5V  |                                                       | -100    | -50  | -25                                              | uA         |

| Input Pull-down<br>Current            | $I_{PD}$           | PA                                                                                         | VDD = 5V  |                                                       | 25      | 50   | 100                                              | uA         |

|                                       | I <sub>DD</sub>    |                                                                                            | VDD = 5V  | fXIN = 16MHz                                          | -       | 2.4  | -                                                | mA         |

|                                       |                    |                                                                                            | VDD = 5V  | EVIN _ OML-                                           | -       | 1.8  | -                                                | А          |

|                                       |                    |                                                                                            | VDD = 3V  | fXIN = 8MHz                                           | -       | 0.9  | -                                                | mA         |

|                                       |                    |                                                                                            | VDD = 5V  | -fXIN = 4MHz -fXIN = 2MHz -fXIN = 1MHz -fXIN = 0.5MHz | -       | 1.2  | -                                                |            |

|                                       |                    |                                                                                            | VDD = 3V  |                                                       | -       | 0.6  | -                                                | mA         |

|                                       |                    | Operating Mode                                                                             | VDD = 5V  |                                                       | -       | 0.9  | -                                                |            |

|                                       |                    |                                                                                            | VDD = 3V  |                                                       | -       | 0.5  | -                                                | mA         |

| Power                                 |                    |                                                                                            | VDD = 5V  |                                                       | -       | 0.8  | -                                                |            |

| supply<br>current                     |                    |                                                                                            | VDD = 3V  |                                                       | -       | 0.4  | -                                                | mA         |

|                                       |                    |                                                                                            | VDD = 5V  |                                                       | -       | 0.7  | -                                                | mA         |

|                                       |                    |                                                                                            | VDD = 3V  | 17111 - 0.514112                                      | -       | 0.3  | -                                                | IIIA       |

|                                       |                    |                                                                                            | VDD = 5V  | RCWDT On                                              | -       | 8    | -                                                | ] <b>,</b> |

|                                       |                    |                                                                                            | VDD = 3V  | TREWDI OII                                            | -       | 5    | -                                                | uA         |

|                                       | $I_{STOP}$         | Stop Mode<br>(Oscillator Stop)                                                             | VDD = 5V  | LVD On                                                | -       | 2    | -                                                |            |

|                                       |                    | (                                                                                          | VDD = 3V  | LVD OII                                               | -       | 1    | -                                                | uA         |

|                                       |                    |                                                                                            | VDD=5V/3V | LVD Off                                               |         | -    | 1                                                | uA         |

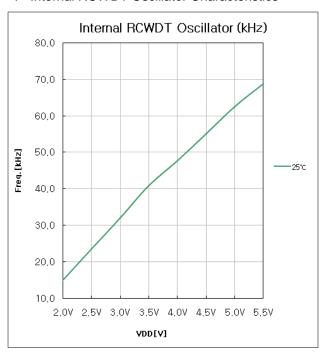

| DCMDT Frequency                       | _                  | DCMDT                                                                                      | VDD = 5V  |                                                       | 32      | 64   | 128                                              |            |

| RCWDT Frequency                       | F <sub>RCWDT</sub> | RCWDT                                                                                      | VDD = 3V  |                                                       | 16      | 32   | 64                                               | KHz        |

| RAM retention supply voltage          | V <sub>RET</sub>   |                                                                                            |           |                                                       | 0.7     |      |                                                  | V          |

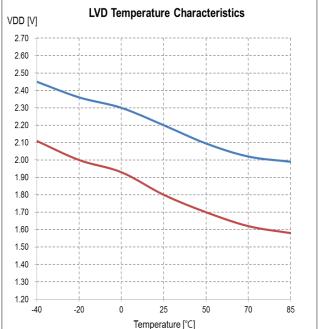

| Low Voltage                           |                    | LVDS=1 (in the Configuration Bits), Ta=25°C<br>LVDS=0 (in the Configuration Bits), Ta=25°C |           |                                                       | 1.6     | 1.8  | 2.0                                              | V          |

| Detection                             | LVD                |                                                                                            |           |                                                       | 2.0     | 2.2  | 2.6                                              | V          |

| Voltage Detection                     | V <sub>VDI1</sub>  |                                                                                            |           | <del>-</del> -                                        | -       | 2.2  | -                                                | V          |

| Voltage Detection<br>Indication Level |                    | Voltage detection indicator level 1  Voltage detection indicator level 2                   |           |                                                       | _       | 3.3  | <del>                                     </del> | V          |

#### \* Typical Characteristics

This graphs provided in this section are for design guidance only and are not tested or guaranteed.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean  $+ 3\sigma$ ) and (mean  $- 3\sigma$ ) respectively where  $\sigma$  is standard deviation.

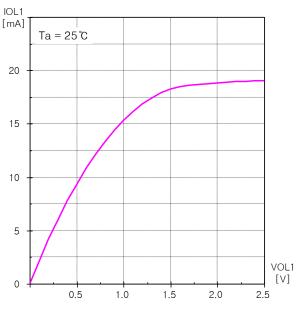

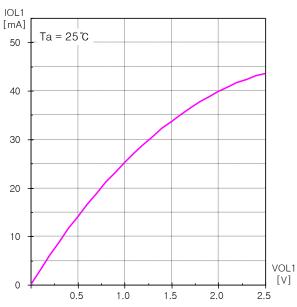

#### ► IOL1 vs. VOL1 (at T=25°C)

IOL1-VOL1, VDD=3.0V

IOL1-VOL1, VDD=5.0V

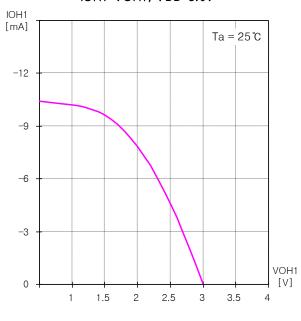

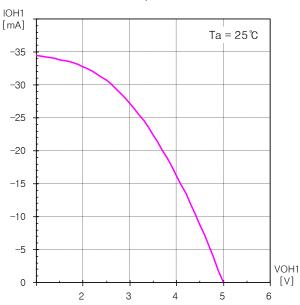

#### ► <u>IOH1 vs. VOH1 (at T=25°C)</u>

IOH1-VOH1, VDD=3.0V

IOH1-VOH1, VDD=5.0V

#### ▶ Internal RC Oscillator Characteristics

#### ▶ Internal RCWDT Oscillator Characteristics

#### ► Low Voltage Detection (Temperature Characteristics)

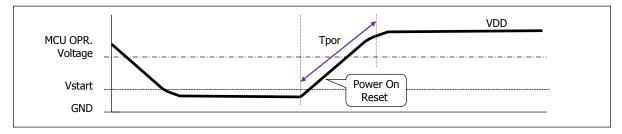

### 1.7.5. POR(Power on Reset) Electrical Characteristics (VDD=5.5V~2.0V, VSS=0V, Ta = -40°C~85°C)

| Parameter               | Symbol   | Condition       | S    | Unit |     |       |  |

|-------------------------|----------|-----------------|------|------|-----|-------|--|

| Parameter               | Эушьог   | Condition       | MIN  | TYP  | MAX | UIIIL |  |

| DOD Stort voltage       | \/otart* | Tpor > 0.35V/ms | VSS  | -    | 0.2 | ٧     |  |

| POR Start voltage       | Vstart*  | Tpor > 0.05V/ms | -    | -    | VSS | ٧     |  |

| VDD Voltage Rising Time | Tpor*    |                 | 0.05 | -    | -   | V/ms  |  |

<sup>\*)</sup> These parameters are presented for design guidance only and not tested or guaranteed.

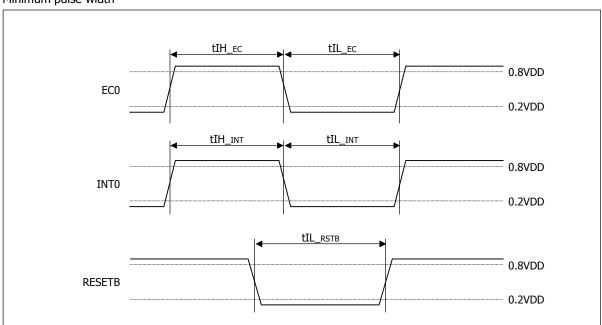

## 1.7.6. AC Characteristics (Ta = $25^{\circ}$ C)

| Parameter                  | Cumbal   | Pin    | Ş    | Unit |      |       |

|----------------------------|----------|--------|------|------|------|-------|

| Parameter                  | Symbol   | PIII   | min. | typ. | max. | Ullit |

| Internal clock cycle time  | tCP      | -      | 62.5 | 250  | 1000 | ns    |

| System clock cycle time    | tSYS     | -      |      | 4    |      | tCP   |

| External pulse width High  | tIH_EC   | EC0    | 1    |      |      | tCP   |

| External pulse width Low   | tIL_EC   | EC0    | 1    |      |      | tCP   |

| Externa pulse width Low    | tIL_RSTB | RESETB | 8    |      |      | tSYS  |

| Interrupt pulse width High | tIH_INT  | INT0   | 2    |      |      | tSYS  |

| Interrupt pulse width Low  | tIL_INT  | INT0   | 2    |      |      | tSYS  |

#### Minimum pulse width

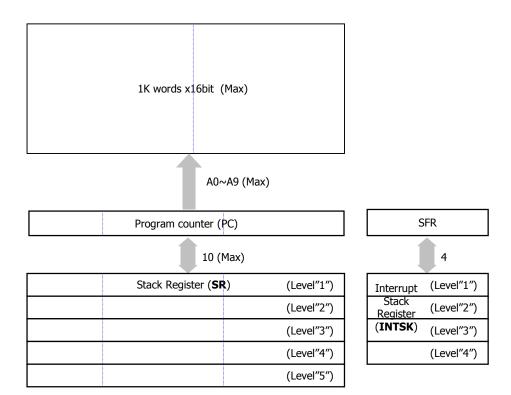

#### 2.1. Program Memory

The ADAM46P20XX can address maximum 2Kbytes (1K words  $\times$  16bits) for program memory. Program counter PC (A0 $\sim$ A9) is used to address the whole area of program memory having an instruction (16bits) to be next executed.

The program memory consists of 1K words.

The program memory is composed as shown below.

Fig 2-1 Configuration of Program Memory

#### 2.2. Address Register

The following registers are used to address the ROM.

#### • Program counter (PC):

Available for addressing word on each page.

#### • Stack register (SR):

Stores returned-word address in the subroutine call mode.

#### 2.2.1 Program counter:

This 10-bit binary counter increments for fetching a word to be addressed in the currently addressed page having an instruction to be next executed.

For easier programming, at turning on the power, the program counter is

reset to the zero location(0000H). Then the program counter specifies the next address. When BR, CAL or RET instructions are decoded, the switches on each step are turned off not to update the address. Then, for BR or CAL, address data are taken in from the instruction operands (A0 to A9), or for RET, and address including page address is fetched from stack register No. 1.

#### 2.2.2. Stack register (SR)

The address stack register (ADS) stores a return address when the subroutine call instruction is executed or interrupt is acknowledged.

If subroutine or interrupts are nested to more than 5 levels, internal reset is occurred.

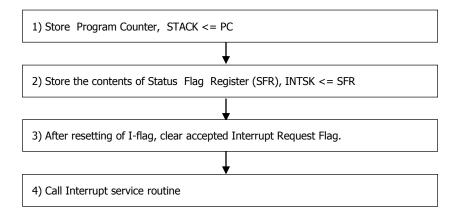

The interrupt stack register(INTSK) saves the contents of Status Flag Register (SFR) when an interrupt is acknowledged.

The saved contents are restored when an interrupt return(RETI) instruction is executed. INTSK saves data each time an interrupt is acknowledged.

The programmer must keep in mind that the level of INTSK is 4. So, if more over 4 levels of interrupt occur, the first stored data is lost. There is different result between Stack overflow and interrupt stack overflow.

When clearing SP (Stack Pointer) with using "SPC" instruction, interrupt processing must be inhibited before "SPC".

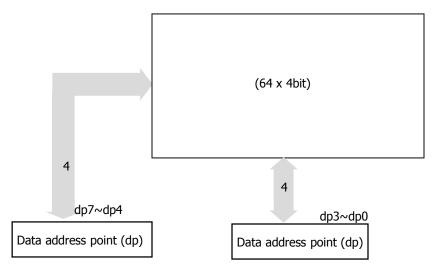

#### 2.3. Data Memory (RAM)

64 nibbles (64  $\times$  4bits) is incorporated for storing data.

Fig 2-2 Data Memory

### 2.3.1. Data memory(RAM) addressing method

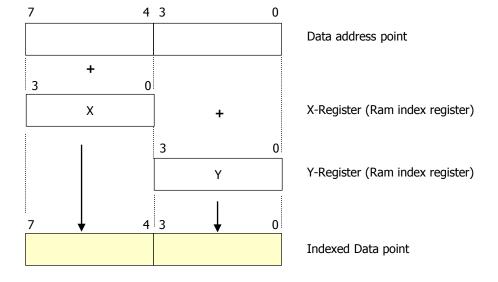

The whole data memory area is directly addressed by 8-bit ram data address point (dp).

Index data memory addressing is available using X-register and Y-register. In this case, X-register is added upper 4bit of data point and Y-register is added lower 4bit of data point.

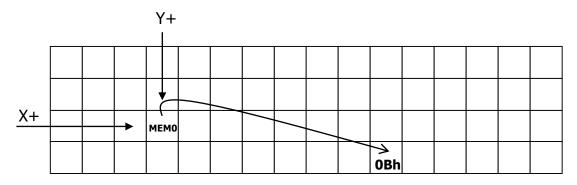

# 2.3.2. Data memory(RAM) data addressing example Program

Fig 2-3 Data Memory Map

Below program example is guidance for understanding the flow of index data memory addressing.

| MEM0 EQU                                      | 023h                                    | ; Defining RAM Address                                                                                                                                                                |

|-----------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDM<br>LYI<br>LXI<br>LDA<br>EIX<br>LDM<br>DIX | MEM0,#0Bh<br>#7<br>#1<br>MEM0<br>MEM0,A | ; [23h] = #0Bh<br>; Setting Y register as #07h<br>; Setting X register as #01h<br>; A = #0Bh == [MEM0]<br>; Index Enable<br>; [3Ah] == [Indexed Addressed Ram] = A<br>; Index Disable |

Result after executing is

MEM0 = #0Bh

[MEM0 + X + Y] = = [3Ah] = #0Bh

#### 2.4. General Function Registers

#### 2.4.1. X-register (X)

X-register is consist of 4 bits, X-register is used for data memory indexing register.

#### 2.4.2. Y-register (Y)

Y-register is consist of 4 bits. It can used for a general-purpose register. Y-register also used for data memory indexing register.

#### 2.4.2. Accumulator (ACC)

The 4-bit register for holding data and calculation results.

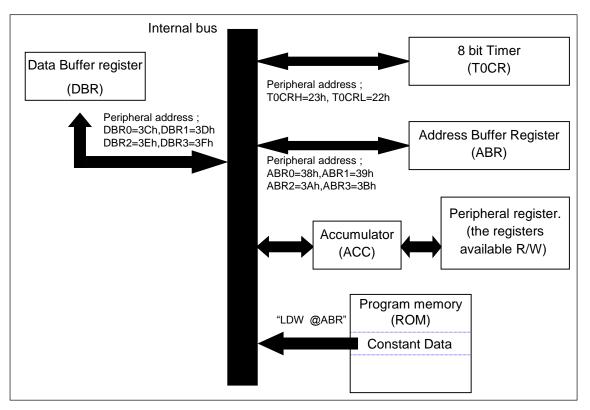

#### 2.4.3. Peripheral Address Register(PAR)

The 6-bit address register for addressing peripheral registers including address buff register(ABR), data buff register (DBR).

#### 2.4.4. Address Buff Register (ABR)

The 16-bit register for address buffer.

It is composed of 4 registers(ABR0, ABR1, ABR2, ABR3).

It is written-only registers and can not used the instruction of bit manipulation.

The address of Address Buffer Register (ABR) is 38h ~38h on the peripheral register (PAR).

The most important function of ABR is ROM address pointer.

If ROM address point is 345h, each ABR must be written as ABR3=0h, ABR2=3h, ABR1=4h, ABR0=5h.

ABR must be used for reading data from ROM. The data pointed by ABR is read to DBR.

\* Caution: Before using ABR, ABR3 register must be always initialized("LRI ABR3,#0").

#### 2.4.5. DATA Buff Register (DBR)

The 16-bit register for Data buffer.

It is composed of 4 registers(DBR0, DBR1, DBR2, DBR3) x 4bit.

The address of Data Buffer Register (DBR) is 3Ch ~3Fh on the peripheral register (PAR).

It is read-only registers and can not used the instruction of bit manipulation.

#### 2.5. Function of Data Buff Register(DBR)

The most important function of DBR is intermediate (window) buffer for transferring data between peripheral registers and reading data from ROM.

When the data of ROM is read by "LDW @ABR", one word of ROM is fetched to DBR.

The MSB of ROM data is written to DBR3 and LSB to DBR0.

If the data of pointed ROM is 1234h, each DBR has the data as DBR0 = 4h, DBR1 = 3h, DBR2 = 2h and DBR3 = 1h.

DBR is also used for reading some peripheral register data by 8bit unit.

The peripheral registers is TOCR.

Note) HEX. File maps the data as big endian type. Be careful to read the ROM data.

When the programmer assigns the data like below, the ROM data is mapped as below.

DB 12h, 34h → ROM data = 1234h

Fig 2-4 The internal Data flow among DBR, ABR, registers and ROM

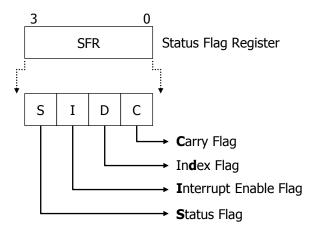

#### 2.6. Status Flag Registers (SFR)

Status Flag Register (SFR) consists of 4-bit register.

Each of the flags show the post state of operation and the flags determining the CPU operation, initialized as 8h in reset state.

When an interrupt is occurred, the value of SFR keep the value of pre-interrupt except for I flag. So, be careful to initialize the SFR status for getting reliable result in Interrupt sub-routine.

#### 2.6.1 Carry flag (C)

- Carry flag bit is set when there is carry or borrow After executing ADDC / SUBC / ARRC/ARLC instructions.

- Set by SETC and clear by CLRC.

- Load from the assigned bit of Peripheral Registers by LDC

- Transfer to the assigned bit of Peripheral Registers by STC

#### 2.6.2 Index flag (D)

- The control bit of ram data address point indexed or not.

- X-register and Y-register is used for index addressing.

- Set and cleared by EIX, DIX.

#### 2.6.3 Interrupt enable flag (I)

- Master enable flag of interrupt.

- Set and cleared by EI, DI

- This Flag immediately becomes "0" when an interrupt is served.

#### 2.6.4 Status flag (S)

- According to the condition after executing an instruction , set or clear.

- Can not be set or clear by any instruction.

- This Flag decides whether operation of BR and CALL would be done or not.

- Initialized as "1" in reset state.

# 2.7. Peripheral Registers

| Peripheral | Function Registers                  | I riedu   Symbol E |        | RESET Value |

|------------|-------------------------------------|--------------------|--------|-------------|

| Address    | Turisticii riegistare               | Write              | Cymbol | 3 2 1 0     |

| 00 h       | PORT PA DATA REG.                   | R/W                | *PADR  | F           |

| 01 h       | PORT PA PULL-UP SELECTION REG.      | W                  | PAPU   | F           |

| 02 h       | PORT PA OPEN DRAIN SELECTION REG.   | W                  | PAOD   | F           |

| 03 h       | PORT PA DIRECTION REG.              | R/W                | PADD   | 0           |

| 04 h       | PORT PA STOP RELEASE SELECTION REG. | W                  | PAST   | F           |

| 05 h       | PORT PA FUNCTION SELECTION REG.     | W                  | PAFN   | 0           |

| 06 h       | PORT PA PULL-DOWN SELECTION REG.    | W                  | PAPD   | 0           |

| 07 h       | Reserved                            |                    |        |             |

| 08 h       | PORT PB DATA REG.                   | R/W                | *PBDR  | F           |

| 09 h       | PORT PB PULL-UP SELECTION REG.      | W                  | PBPU   | F           |

| 0A h       | PORT PB OPEN DRAIN SELECTION REG.   | W                  | PBOD   | F           |

| 0B h       | PORT PB DIRECTION REG.              | R/W                | PBDD   | 0           |

| 0C h       | PORT PB STOP RELEASE SELECTION REG. | W                  | PBST   | F           |

| 0D h       | PORT PB FUNCTION SELECTION REG.     | W                  | PBFN   | 0           |

| 0E h       | Reserved                            |                    |        |             |

| 0F h       | Reserved                            |                    |        |             |

| 10 h       | PORT PD DATA REG.                   | R/W                | *PDDR  | F           |

| 11 h       | PORT PD PULL-UP SELECTION REG.      | W                  | PDPU   | F           |

| 12 h       | Reserved                            |                    |        |             |

| 13 h       | Reserved                            |                    |        |             |

| 14 h       | Reserved                            |                    |        |             |

| 15 h       | Reserved                            |                    |        |             |

| 16 h       | EXT. INTERRUPT EDGE SELECTION REG.  | W                  | IEDS0  | 0           |

| 17 h       | SYSTEM CONTROL REG.                 | W                  | SCTLR  | 0           |

| 18 h       | PORT PD OPEN DRAIN SELECTION REG.   | W                  | PDOD   | F           |

| 19 h       | PORT PD DIRECTION REG.              | R/W                | PDDD   | 0           |

| 1A h       | Reserved                            |                    |        |             |

| 1B h       | Reserved                            |                    |        |             |

| 1C h       | INTERRUPT REQUEST FLAG REG. 0       | R/W                | IRQR0  | 0           |

| 1D h       | Reserved                            |                    |        |             |

| 1E h       | INTERRUPT ENABLE REG. 0             | R/W                | IENR0  | 0           |

| 1F h       | Reserved                            |                    |        |             |

Note1> '-' is reserved bit , it must be read to "0". Note2> \* Using the bit access Instruction, bit is read-modified operation (SETR1/CLRR1/STC Instructions)

27

| Peripheral | Function Registers                   | Read  | Symbol | RESET Value |

|------------|--------------------------------------|-------|--------|-------------|

| Address    |                                      | Write | -,     | 3210        |

| 20 h       | TIMER-0 MODE REG. 0                  | R/W   | T0MR0  | 0           |

| 21 h       | TIMER-0 MODE REG. 1                  | W     | T0MR1  | 0           |

|            | TIMER-0 DATA 0 LOW REG.              | W     | T0D0L  | undefined   |

| 22 h       | TIMER-0 COUNT REG. LOW               | R     | T0CRL  | undefined   |

|            | TIMER-0 CAPTURE LOW REG.             | R     | T0CPL  | undefined   |

|            | TIMER 0 DATA 0 HIGH REG.             | W     | T0D0H  | undefined   |

| 23 h       | TIMER 0 COUNT REG. HIGH              | R     | T0CRH  | undefined   |

|            | TIMER-0 CAPTURE HIGH REG.            | R     | ТОСРН  | undefined   |

| 24 h       | TIMER-0 DATA 1 LOW REG.              | W     | T0D1L  | undefined   |

| 25 h       | TIMER-0 DATA 1 HIGH REG.             | W     | T0D1H  | undefined   |

| 26 h       | Reserved                             |       |        |             |

| 27 h       | Reserved                             |       |        |             |

| 28 h       | Reserved                             |       |        |             |

| 29 h       | Reserved                             |       |        |             |

| 2A h       | Reserved                             |       |        |             |

| 2B h       | Reserved                             |       |        |             |

| 2C h       | Reserved                             |       |        |             |

| 2D h       | Reserved                             |       |        |             |

| 2E h       | Reserved                             |       |        |             |

| 2F h       | Reserved                             |       |        |             |

| 30 h       | Reserved                             |       |        |             |

| 31 h       | Reserved                             |       |        |             |

| 32 h       | Reserved                             |       |        |             |

| 00.1       | VTG. DETECTION INDICATOR ENABLE REG. | W     | VDIER  | 0           |

| 33 h       | VTG DETECTION INDICATOR FLAG REG.    | R     | VDIR   | 00          |

| 34 h       | Reserved                             |       |        |             |

| 35 h       | Reserved                             |       |        |             |

| 36 h       | Reserved                             |       |        |             |

| 37 h       | WATCH-DOG TIMER CONTROL REG.         | W     | WDTCR  | 0           |

| 38 h       | ADDRESS BUFF REGISTER 0              | W     | ABR0   | undefined   |

| 39 h       | ADDRESS BUFF REGISTER 1              | W     | ABR1   | undefined   |

| 3A h       | ADDRESS BUFF REGISTER 2              | W     | ABR2   | undefined   |

| 3B h       | ADDRESS BUFF REGISTER 3              | W     | ABR3   | undefined   |

| 3C h       | DATA BUFF REGISTER 0                 | R     | DBR0   | undefined   |

| 3D h       | DATA BUFF REGISTER 1                 | R     | DBR1   | undefined   |

| 3E h       | DATA BUFF REGISTER 2                 | R     | DBR2   | undefined   |

| 3F h       | DATA BUFF REGISTER 3                 | R     | DBR3   | undefined   |

Note1> '-' is reserved bit , it must be read to "0". Note2> 'ABR3' must be initialized before using ABR (LDW @ABR, BR @ABR, CALL @ABR).

The ADAM46P20XX has 12 I/O ports which are PA (4 I/O), PB (4 I/O), PD (4 I/O).

PA and PB Port have Stop Release selection register.

Pull-up resistor of PA, PB and PD ports can be selectable by program.

Pull-down resistor of PA ports can be selectable by program.

PA, PB and PD ports contains data direction register which controls I/O and data register which stores port data.

PA, PB and PD Ports have Open Drain selection register and Data register.

\*PB1 is Open Drain output only.

#### I/O Ports Registers

| Port    | Data<br>Reg. | Pull-up<br>Reg. | Open-Drain<br>Reg. | Direction<br>Reg. | Stop Release<br>Reg. | Function<br>Reg. | Pull-down<br>Reg. |

|---------|--------------|-----------------|--------------------|-------------------|----------------------|------------------|-------------------|

| port PA | PADR         | PAPU            | PAOD               | PADD              | PAST                 | PAFN             | PAPD              |

| port PB | PBDR         | PBPU            | PBOD               | PBDD              | PBST                 | PBFN             | _                 |

| port PD | PDDR         | PDPU            | PDOD               | PDDD              | -                    | -                | -                 |

| R/W           | R/W  | W       | W       | R/W   | W       | W         | W       |

|---------------|------|---------|---------|-------|---------|-----------|---------|

| Initial value | 1111 | 1111    | 1111    | 0000  | 1111    | 0000      | 0000    |

| default       | fh   | disable | disable | input | disable | I/O ports | disable |

#### 3.1. Port PA

| Pin Name           | Port<br>Selection | Function Selection                                        |

|--------------------|-------------------|-----------------------------------------------------------|

| PA0/KSA0           | PA0 (I/O)         | KSA0 Input                                                |

| PA1/KSA1           | PA1 (I/O)         | KSA1 Input                                                |

| PA2/KSA2/INT0(EC0) | PA2 (I/O)         | KSA2 Input/ External Interrupt Input/ Event counter input |

| PA3/KSA3           | PA3 (I/O)         | KSA3 Input                                                |

#### 3.1.1. PA Data Register (PADR)

| bit           | 3     | 2     | 1     | 0     | _   |

|---------------|-------|-------|-------|-------|-----|

| PADR          | PADR3 | PADR2 | PADR1 | PADR0 | 00h |

| Initial value | 1     | 1     | 1     | 1     | 1   |

| R/W           | R/W   | R/W   | R/W   | R/W   |     |

PA data register (PADR) is 4-bit register to store data of port PA.

When set as the output state by PADD, and data is written in PADR, data is outputted into PA pin. When set as the input state, input state of pin is read. The initial value of PADR is "Fh" in reset state. At output state, if port PA is read, PA Data Register (PADR) is read instead of port PA.

#### 3.1.2. PA Pull-up Resistor Control Register (PAPU)

| bit           | 3     | 2     | 1     | 0     |     |

|---------------|-------|-------|-------|-------|-----|

| PAPU          | PAPU3 | PAPU2 | PAPU1 | PAPU0 | 01h |

| Initial value | 1     | 1     | 1     | 1     |     |

| R/W           | W     | W     | W     | W     |     |

PA pull-up resistor control register (PAPU) is 4-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If PAPU is selected as "0", pull-up is enabled and if selected as "1", it is disabled. PAPC is write-only register and initialized as "Fh" in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

#### 3.1.3. PA Open Drain Assign Register (PAOD)

| bit           | 3     | 2     | 1     | 0     |     |

|---------------|-------|-------|-------|-------|-----|

| PAOD          | PAOD3 | PAOD2 | PAOD1 | PAOD0 | 02h |

| Initial value | 1     | 1     | 1     | 1     |     |

| R/W           | W     | W     | W     | W     |     |

PA Open Drain Assign Register (PAOD) is 4-bit register, and can assign PA port as open drain output port each bit If PAOD is selected as "0", port PA is open drain output, and if selected as "1", it is push-pull output. PAOD is write-only register and initialized as "Fh" in reset state.

#### 3.1.4. PA I/O Data Direction Register (PADD)

| bit           | 3     | 2     | 1     | 0     |     |

|---------------|-------|-------|-------|-------|-----|

| PADD          | PADD3 | PADD2 | PADD1 | PADD0 | 03h |

| Initial value | 0     | 0     | 0     | 0     |     |

| R/W           | R/W   | R/W   | R/W   | R/W   |     |

PA I/O Data Direction Register (PADD) is 4-bit register, and can assign input state or output state to each bit. If PADD is "0", port PA is in the input state, and if "1", it is in the output state. Since PADD is initialized as "0h" in reset state, the whole port PA becomes input state.

#### 3.1.5. PA Stop Release Selection Register (PAST)

| bit           | 3     | 2     | 1     | 0     |                  |

|---------------|-------|-------|-------|-------|------------------|

| PAST          | PAST3 | PAST2 | PAST1 | PAST0 | 0 <del>4</del> h |

| Initial value | 1     | 1     | 1     | 1     |                  |

| R/W           | W     | W     | W     | W     |                  |

PA Stop Release Selection Register (PAST) is 4-bit register, and can assign stop release pin or not. If PAST is selected as "0", stop release function is enabled and if selected as "1", it is disabled. PAST is write-only register and initialized as "Fh" in reset state. The Stop Release function is automatically disabled, if corresponding port is selected as output.

#### 3.1.6. PA Function Selection Register (PAFN)

| bit           | 3 | 2     | 1 | 0 |     |

|---------------|---|-------|---|---|-----|

| PAFN          | - | PAFN2 | - | - | 05h |

| Initial value | - | 0     | - | - |     |

| R/W           | W | W     | W | W |     |

#### Selection Mode of PAFN

| Bit Name |   | Selection Mode                    | Remarks   |

|----------|---|-----------------------------------|-----------|

| -        | - | _                                 |           |

| DACNO    | 0 | 1/0                               |           |

| PAFN2    | 1 | Interrupt & Event count Selection | INT0(EC0) |

| -        | - | _                                 |           |

| _        | - | _                                 |           |

#### 3.1.7. PA Pull-Down Resistor Selection Register (PAPD)

| bit           | 3     | 2     | 1     | 0     | _   |

|---------------|-------|-------|-------|-------|-----|

| PAPD          | PAPD3 | PAPD2 | PAPD1 | PAPD0 | 06h |

| Initial value | 0     | 0     | 0     | 0     | •   |

| R/W           | W     | W     | W     | W     |     |

PA pull-down resistor control register (PAPD) is 4-bit register and can control pull-down on or off each bit. If PAPD is selected as "1", pull-down is enabled and if selected as "0", it is disabled. PAPD is write-only register and initialized as "0h" in reset state.

#### 3.2. Port PB

| Pin Name        | Port<br>Selection | Function Selection        |

|-----------------|-------------------|---------------------------|

| PB0/PWM0/KSB0   | PB0 (I/O)         | PWM0 Output / KSB0 Input  |

| PB1/RESETB/KSB1 | PB1 (I/O)         | RESETB Input / KSB1 Input |

| PB2/CLO/KSB2    | PB2 (I/O)         | CLO Output / KSB2 Input   |

| PB3/KSB3        | PB3 (I/O)         | KSB3 Input                |

#### 3.2.1. PB Data Register (PBDR)

| bit           | 3     | 2     | 1     | 0     |     |

|---------------|-------|-------|-------|-------|-----|

| PBDR          | PBDR3 | PBDR2 | PBDR1 | PBDR0 | 08h |

| Initial value | 1     | 1     | 1     | 1     | •   |

| R/W           | R/W   | R/W   | R/W   | R/W   |     |

PB data register (PBDR) is 4-bit register to store data of port PB.

When set as the output state by PBDD, and data is written in PBDR, data is outputted into PB pin. When set as the input state, input state of pin is read. The initial value of PBDR is "Fh" in reset state. At output state, if port PB is read, PB Data Register (PBDR) is read instead of port PB.

#### 3.2.2. PB Pull-up Resistor Control Register (PBPU)

| bit           | 3     | 2     | 1     | 0     | _   |

|---------------|-------|-------|-------|-------|-----|

| PBPU          | PBPU3 | PBPU2 | PBPU1 | PBPU0 | 09h |

| Initial value | 1     | 1     | 1     | 1     |     |

| R/W           | W     | W     | W     | W     |     |

PB pull-up resistor control register (PBPU) is 4-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If PBPU is selected as "0", pull-up is enabled and if selected as "1", it is disabled. PBPU is write-only register and initialized as "Fh" in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

#### 3.2.3. PB Open Drain Assign Register (PBOD)

| bit           | 3     | 2     | 1     | 0    | _   |

|---------------|-------|-------|-------|------|-----|

| PBOD          | PBOD3 | PBOD2 | PBOD1 | PBOD | 0Ah |

| Initial value | 1     | 1     | 1     | 1    | •   |

| R/W           | W     | W     | W     | W    |     |

PB Open Drain Assign Register (PBOD) is 4-bit register, and can assign PB port as open drain output port each bit If PBOD is selected as "0", port PB is open drain output, and if selected as "1", it is push-pull output. PBOD is write-only register and initialized as "Fh" in reset state.

#### 3.2.4. PB I/O Data Direction Register (PBDD)

| bit           | 3     | 2     | 1     | 0     |     |

|---------------|-------|-------|-------|-------|-----|

| PBDD          | PBDD3 | PBDD2 | PBDD1 | PBDD0 | 0Bh |

| Initial value | 0     | 0     | 0     | 0     |     |

| R/W           | R/W   | R/W   | R/W   | R/W   |     |

PB I/O Data Direction Register (PBDD) is 4-bit register, and can assign input state or output state to each bit. If PBDD is "0", port PB is in the input state, and if "1", it is in the output state. Since PBDD is initialized as "0h" in reset state, the whole port PB becomes input state.

#### 3.2.5. PB Stop Release Selection Register (PBST)

| bit           | 3     | 2     | 1     | 0     |     |

|---------------|-------|-------|-------|-------|-----|

| PBST          | PBST3 | PBST2 | PBST1 | PBST0 | 0Ch |

| Initial value | 1     | 1     | 1     | 1     |     |

| R/W           | W     | W     | W     | W     |     |

PB Stop Release Selection Register (PBST) is 4-bit register, and can assign stop release pin or not. If PBST is selected as "0", stop release function is enabled and if selected as "1", it is disabled. PBST is write-only register and initialized as "Fh" in reset state. The Stop Release function is automatically disabled, if corresponding port is selected as output.

#### 3.2.6. PB Function Selection Register (PBFN)

| bit           | 3 | 2     | 1 | 0     |     |

|---------------|---|-------|---|-------|-----|

| PBFN          | - | PBFN2 | 1 | PBFN0 | 0Dh |

| Initial value | - | 0     | - | 0     |     |

| R/W           | W | W     | W | W     |     |

#### Selection Mode of PBFN

| Bit Name |   | Selection Mode Remar           |      |

|----------|---|--------------------------------|------|

| -        | - | _                              |      |

| סטבאוס   | 0 | I/O                            |      |

| PBFN2    | 1 | CLO(fosc) Output Selection     | CLO  |

| -        | - | _                              |      |

| DDENO    | 0 | 1/0                            |      |

| PBFN0    | 1 | PWM0 (Timer0) Output Selection | PWM0 |

#### 3.3. Port PD

| Pin Name | Port<br>Selection | Function Selection |

|----------|-------------------|--------------------|

| PD0      | PD0 (I/O)         | _                  |

| PD1      | PD1 (I/O)         | -                  |

| PD2      | PD2 (I/O)         | _                  |

| PD3      | PD3 (I/O)         | _                  |

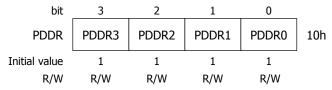

#### 3.3.1. PD Data Register (PDDR)

PD data register (PDDR) is 4-bit register to store data of port PD.

When set as the output state by PDDD, and data is written in PDDR, data is outputted into PD pin. When set as the input state, input state of pin is read. The initial value of PDDR is "Fh" in reset state. At output state, if port PD is read, PD Data Register (PDDR) is read instead of port PD.

#### 3.3.2. PD Pull-up Resistor Control Register (PDPU)

| bit           | 3     | 2     | 1     | 0     |     |

|---------------|-------|-------|-------|-------|-----|

| PDPU          | PDPU3 | PDPU2 | PDPU1 | PDPU0 | 11h |

| Initial value | 1     | 1     | 1     | 1     |     |

| R/W           | W     | W     | W     | W     |     |

PD pull-up resistor control register (PDPU) is 4-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If PDPU is selected as "0", pull-up is enabled and if selected as "1", it is disabled. PDPU is write-only register and initialized as "Fh" in reset state. The pull-up is automatically disabled, if corresponding port is selected as output.

#### 3.3.3. PD Open Drain Assign Register (PDOD)

| bit           | 3     | 2     | 1     | 0     |     |

|---------------|-------|-------|-------|-------|-----|

| PDOD          | PDOD3 | PDOD2 | PDOD1 | PDOD0 | 18h |

| Initial value | 1     | 1     | 1     | 1     |     |

| R/W           | W     | W     | W     | W     |     |

PD Open Drain Assign Register (PDOD) is 4-bit register, and can assign PD port as open drain output port each bit If PDOD is selected as "0", port PD is open drain output, and if selected as "1", it is pushpull output. PDOD is write-only register and initialized as "Fh" in reset state.

#### 3.3.4. PD I/O Data Direction Register (PDDD)

| bit           | 3     | 2     | 1     | 0     |     |

|---------------|-------|-------|-------|-------|-----|

| PDDD          | PDDD3 | PDDD2 | PDDD1 | PDDD0 | 19h |

| Initial value | 0     | 0     | 0     | 0     |     |

| R/W           | R/W   | R/W   | R/W   | R/W   |     |

PD I/O Data Direction Register (PDDD) is 4-bit register, and can assign input state or output state to each bit. If PDDD is "0", port PD is in the input state, and if "1", it is in the output state. Since PDDD is initialized as "0h" in reset state, the whole port PD becomes input state.

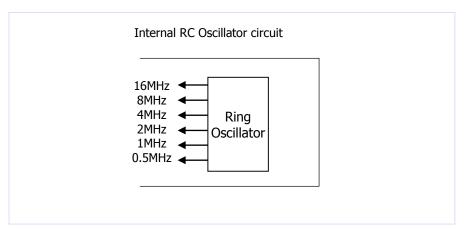

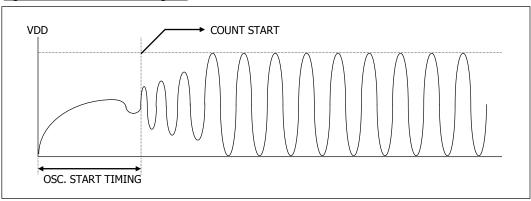

## 4. Oscillation Circuit

#### 4.1. Oscillation Circuit

Clock from oscillation circuit makes CPU clock via clock pulse generator, and then provide peripheral hardware clock.

There is 1 type of Oscillation circuit and it can be divided in 6 different oscillator option modes. The user can used OTP Configuration Option Bits (OSCS2 through OSCS0) to select one of these 6 types. Refer to Table 4.1.

• IRC : Internal RC Oscillator (6 modes)

Fig.4.1 Oscillator configurations

It is Internal RC Oscillator circuit. The Internal Oscillator is calibrated by calibration option bits. In STOP mode, Internal RC oscillator is stopped.

Below table shows the selection of the oscillator type by OTP Configuration Option Bits (Address 8000h, OSCS2  $\sim$  OSCS0). (Refer to 13.2. Configuration Option Bit Description)

| Table   | 4 1  | Oscillator | Type | and | Modes   | Selection |

|---------|------|------------|------|-----|---------|-----------|

| i abic. | т. т | Oscillator | IVDC | anu | 1,10062 | SCICCIOII |

| OSCS[2:0] |         |         | On sillaton Mandan    |  |

|-----------|---------|---------|-----------------------|--|

| OSCS[2]   | OSCS[1] | OSCS[0] | Oscillator Modes      |  |

| 1         | 1       | 1       | Internal RC 4MHz      |  |

| 1         | 1       | 0       | Internal RC 8MHz      |  |

| 1         | 0       | 1       | Internal RC 16MHz     |  |

| 1         | 0       | 0       | Internal RC 1MHz      |  |

| 0         | 1       | 1       | Internal RC 0.5MHz    |  |

| 0         | 1       | 0       | Internal RC 2MHz      |  |

| 0         | 0       | 1       | Setting is prohibited |  |

| 0         | 0       | 0       |                       |  |

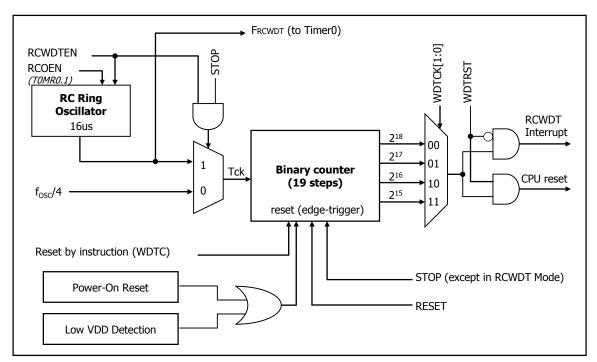

# 5. Watch Dog Timer

### 5.1. Watch Dog Timer (WDT)

Watch dog timer is organized binary of 19 steps. The signal of  $f_{OSC}/4$  cycle comes in the first step of WDT after WDT reset. If this counter was overflowed, reset signal automatically come out so that internal circuit is initialized. The overflow time is initially  $2^{18} \times 4/f_{OSC}$  (262.144ms at  $f_{OSC} = 4.0$ MHz), it is selectable by WDT Control Register (WDTCR). Normally, the binary counter must be reset before the overflow by using reset instruction (WDTC), Power-on reset pulse or Low VDD detection pulse. It is constantly reset in STOP mode. When STOP is released, counting is restarted.

If it's executed the STOP instruction after setting the bit RWDTEN of WDTCR to "1", the Internal RC-Ring Oscillated Watch-dog Timer (RCWDT) mode is activated.

### 5.1.1. WDT Control Register

| bit                  | 3      | 2      | 1      | 0      |     |

|----------------------|--------|--------|--------|--------|-----|

| WDTCR                | WDTRST | RWDTEN | WDTCK1 | WDTCK0 | 37h |

| Initial value<br>R/W | 1<br>W | 0<br>W | 0<br>W | 0<br>W |     |

| WDTRST    | 0  | WDT interrupt enable, when WDT Overflow is occurred.          |

|-----------|----|---------------------------------------------------------------|

| WDIRST    | 1  | System Reset enable, when WDT Overflow is occurred. (default) |

| רואיסדראו | 0  | RCWDT mode disable (Tck = fosc/4)                             |

| RWDTEN    | 1  | RCWDT Oscillator Enable & RCWDT mode enable                   |

|           | 00 | WDT Overflow Time is 2 <sup>18</sup> x Tck                    |

| WDTCK1    | 01 | WDT Overflow Time is 2 <sup>17</sup> × Tck                    |

| WDTCK0    | 10 | WDT Overflow Time is 2 <sup>16</sup> × Tck                    |

|           | 11 | WDT Overflow Time is 2 <sup>15</sup> × Tck                    |

### Reset or Interrupt Wakeup Time (Example)

|            | Tck * 2 <sup>18</sup> | Tck * 2 <sup>17</sup> | Tck * 2 <sup>16</sup> | Tck * 2 <sup>15</sup> | Unit |

|------------|-----------------------|-----------------------|-----------------------|-----------------------|------|

| Tck = 1us  | 262.144               | 131.072               | 65.536                | 32.768                |      |

| Tck = 16us | 4,194.304             | 2,097.152             | 1,048.076             | 524.288               | ms   |

Fig.5.1 Block Diagram of Watch-dog Timer

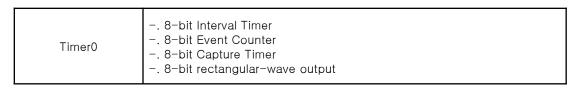

#### 6.1. Timer

#### 6.1.1. Timer operation mode

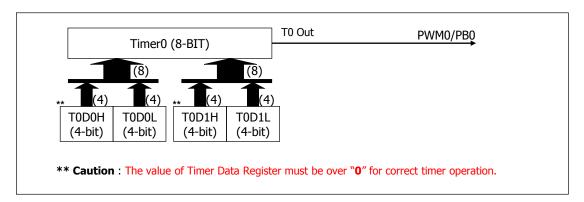

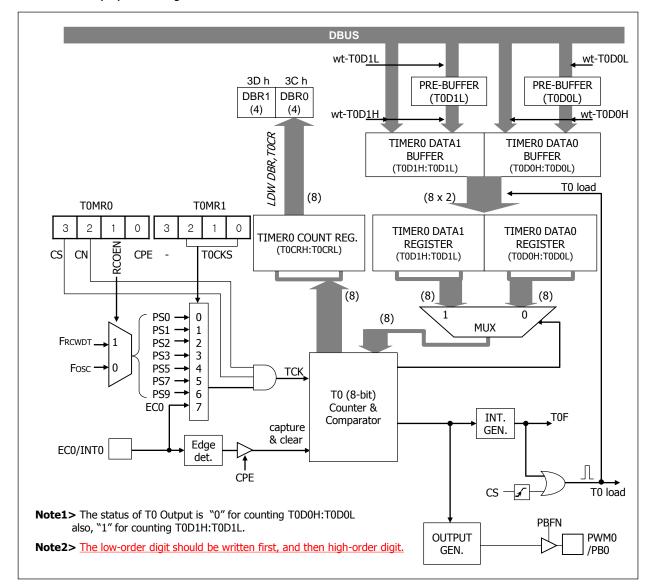

Timer is basically made of Timer Data Register, Timer Mode Register and control circuit. The type of Timer is 8bit binary counter Timer0 (T0).

**Timer0 Data Register** consists of Timer0 Data 0 High Register (T0D0H), Timer0 Data 0 Low Register (T0D0L), Timer0 Data 1 High Register (T0D1H) and Timer0 Data 1 Low Register (T0D1L).

Fig. 6.1 Timer/Counter Block diagram (8-Bit Mode)

### 6.2. Timer0

### 6.2.1. Timer0(T0) Block Diagram

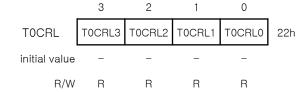

## 6.2.2. Timer0 Control Register

### • Timer0 Mode Register 0 (T0MR0)

|               | 3    | 2    | 1     | 0     | _   |

|---------------|------|------|-------|-------|-----|

| T0MR0         | T0CS | T0CN | RCOEN | T0CPE | 20h |

| initial value | 0    | 0    | 0     | 0     |     |

| R/W           | R/W  | R/W  | R/W   | R/W   |     |

# Selection Mode of T0MR0

| Bit Name |                                 |   | Selection Mode                  | Remarks |

|----------|---------------------------------|---|---------------------------------|---------|

| T000     | Timer0 Clear / start Control    |   | Timer0 Stop                     |         |

| T0CS     |                                 |   | Timer0 Clear and Start          |         |

| T        |                                 | 0 | Timer0 Pause                    |         |

| T0CN     | Timer0 Pause / Continue Control | 1 | Timer0 continue                 |         |

|          |                                 |   | System clock (Fosc)             |         |

| RCOEN    | Input Clock Source selection    | 1 | RCWDT clock (FRCWDT=Typ. 64kHz) |         |

| T0CPE    |                                 |   | Timer/Counter Mode              |         |

|          | Input capture Mode selection    | 1 | Capture Mode                    | ·       |

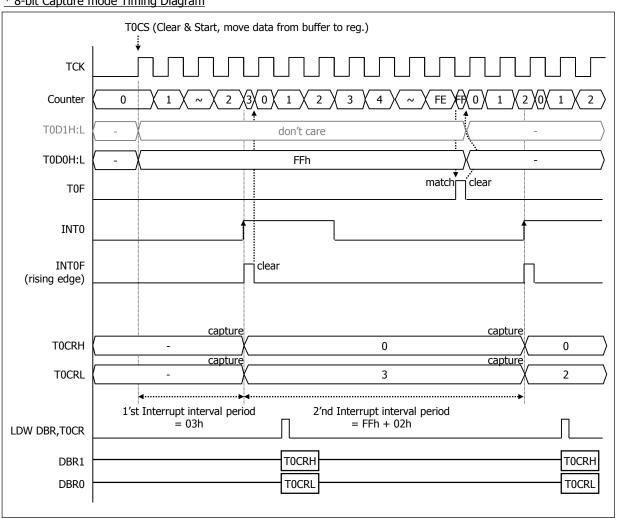

**Note:** Timer 0 only counts with `T0D0H+T0D0L' and can occur the interrupt in every counter overflow, if timer0 operates at 8-bit Capture mode.

## • Timer0 Mode Register 1 (T0MR1)

|               | 3 | 2     | 1     | 0     |     |

|---------------|---|-------|-------|-------|-----|

| T0MR0         | - | T0CK2 | T0CK1 | T0CK0 | 21h |

| initial value | - | 0     | 0     | 0     |     |

| R/W           | W | W     | W     | W     |     |

## Selection Mode of T0MR1

| Bit Name                                |                       |                              | Selection Mode              |                       | Remarks |

|-----------------------------------------|-----------------------|------------------------------|-----------------------------|-----------------------|---------|

| -                                       | -                     | -                            | _                           |                       |         |

|                                         |                       |                              | RCOEN = 0                   | RCOEN=1               |         |

| T0CK2 T0CK1 Input clock selection T0CK0 | 000                   | *PS0 (=Fosc/2 <sup>0</sup> ) | FRCWDT/20                   |                       |         |

|                                         |                       | 001                          | PS1 (=Fosc/2 <sup>1</sup> ) | FRCWDT/2 <sup>1</sup> |         |

|                                         | Input clock selection | 010                          | PS2 (=Fosc/2 <sup>2</sup> ) | FRCWDT/2 <sup>2</sup> |         |

|                                         |                       | 011                          | PS3 (=Fosc/2 <sup>3</sup> ) | FRCWDT/2 <sup>3</sup> |         |

|                                         |                       | 100                          | PS5 (=Fosc/2 <sup>5</sup> ) | FRCWDT/2 <sup>5</sup> |         |

|                                         |                       | 101                          | PS7 (=Fosc/2 <sup>7</sup> ) | FRCWDT/2 <sup>7</sup> |         |

|                                         |                       | 110                          | PS9 (=Fosc/2 <sup>9</sup> ) | FRCWDT/29             |         |

|                                         |                       | 111                          | EC0                         |                       |         |

**Caution :** PS0 must be used only in the case of fosc  $\leq$  8MHz.

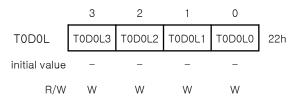

• Timer0 Data0 Register Low (T0D0L)

• Timer0 Count Register Low (T0CRL)

• Timer0 Data0 Register High (T0D0H)

|               | 3      | 2      | 1      | 0      |     |

|---------------|--------|--------|--------|--------|-----|

| T0D0H         | T0D0H3 | T0D0H2 | T0D0H1 | ТОДОНО | 23h |

| initial value | -      | _      | _      | -      |     |

| R/W           | W      | W      | W      | W      |     |

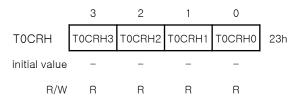

• Timer0 Count Register High (T0CRH)

**Note:** The T0D0x, T0CRx(Timer0 Count Reg.) and T0CPx(Timer0 Capture Reg.) are in same address. In the capture mode, reading operation is read the T0CPx, not T0CRx because path is opened to the T0CPx, and T0D0x is only for writing operation.

• Timer0 Data1 Register Low (T0D1L)

|               | 3      | 2      | 1      | 0      |     |

|---------------|--------|--------|--------|--------|-----|

| T0D1L         | T0D1L3 | T0D1L2 | T0D1L1 | T0D1L0 | 24h |

| initial value | -      | -      | -      | -      |     |

| R/W           | W      | W      | W      | W      |     |

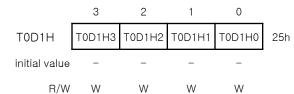

• Timer0 Data1 Register High (T0D1H)

#### 6.2.3. Timer0 Caution

The value of Timer Data Register must be over "0" for correct timer operation.

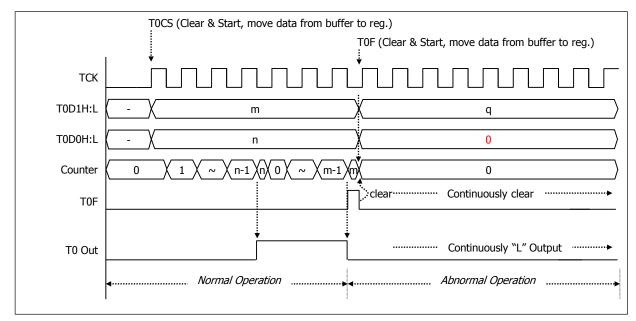

#### 6.2.4. Timer0 Timing Diagram

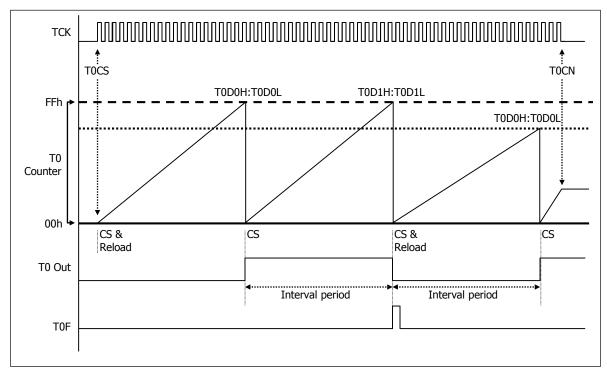

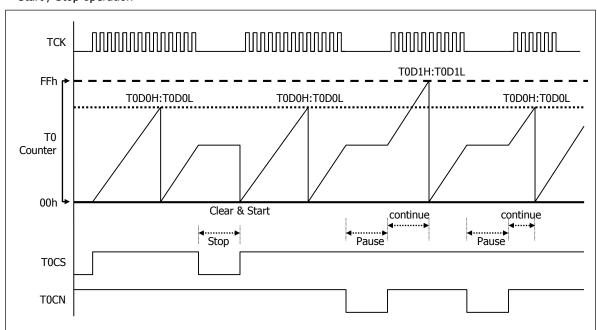

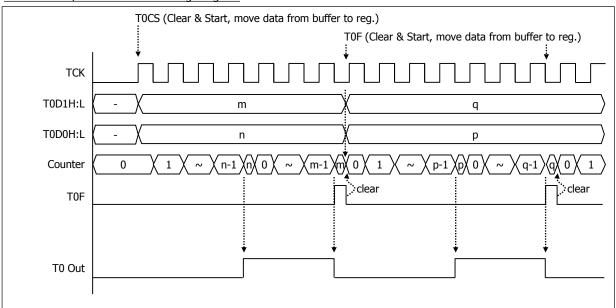

### \* 8-bit Timer/Counter mode Timing Diagram

Note > CS : Timer0 Counter Clear & Start.

Reload : Timer0 Data move from Data buffer to Data register.

### \* Start / Stop operation

# \* 8-bit Timer/Counter mode Timing Diagram

# \* 8-bit Capture mode Timing Diagram

42

#### \* 8-bit PWM mode

Timer0 make the PWM (Pulse Width Modulation) functions without additional mode setting, because they have the Data L Registers(T0D0H+T0D0L) and the Data H Registers(T0D1H+T0D1L). The low pulse width of the PWM output determined by the Data L Registers, and the high pulse width of the PWM output determined by the Data H Registers. The period of the PWM output is the sum of the Data L Registers value and the Data H Registers value.

## PWM Period = Low pulse width + High pulse width

|                  | Timer0                       |  |  |  |

|------------------|------------------------------|--|--|--|

| Low pulse width  | (T0D0H,T0D0L) x Source Clock |  |  |  |

| High pulse width | (T0D1H,T0D1L) x Source Clock |  |  |  |

When main frequency is 4MHz, maximum PWM frequency is shown as below Table.

freq = 4MHz

| Source Clock        | Pulse Wid | th Range  | Duty ratio      | Max. PWM<br>Frequency |  |

|---------------------|-----------|-----------|-----------------|-----------------------|--|

| Source Clock        | Low       | High      | Duty ratio      |                       |  |

| PS0 (000) : 0.25us  | 01h ∼ FFh | 01h ~ FFh | 1/256 ~ 255/256 | 15.6250 kHz           |  |

| PS1 (001) : 0.5us   | <b>↑</b>  | <b>↑</b>  | <b>†</b>        | 7.8125 kHz            |  |

| PS2 (010) : 1.0us   | <b>↑</b>  | <b>↑</b>  | <b>†</b>        | 3.9063 kHz            |  |

| PS3 (011) : 2.0us   | <b>↑</b>  | 1         | <b>†</b>        | 1.9531 kHz            |  |

| PS5 (100) : 8.0us   | <b>↑</b>  | <b>↑</b>  | <b>†</b>        | 0.4883 kHz            |  |

| PS7 (101) : 32.0us  | <b>↑</b>  | 1         | <b>†</b>        | 0.1220 kHz            |  |

| PS9 (110) : 128.0us | <u></u>   | 1         | <b>†</b>        | 0.0305 kHz            |  |

| EC0 (111)           | <b>↑</b>  | <b>↑</b>  | <b>†</b>        | depends on EC0        |  |

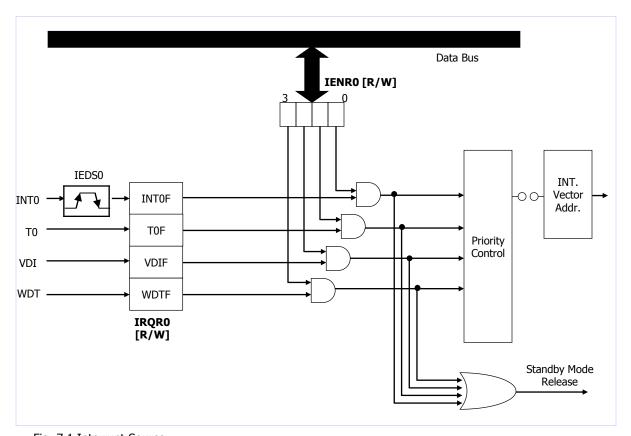

The ADAM46P20XX contains 4 interrupt sources; 1 externals and 3 internals. Nested interrupt services with priority control is also possible.

- ▶ 4 interrupt source (1Ext, 1Timer, 1VDI, 1WDT)

- ▶ 4 interrupt vector

- ▶ 4 level nested interrupt control is possible.

- ▶ Read of interrupt request flag are possible.

- ▶ In interrupt accept, request flag is automatically cleared.

Interrupt Enable Register (IENR0), Interrupt Request Register (IRQR0) and priority circuit. Interrupt function block diagram is shown in Fig. 7.1

Fig. 7.1 Interrupt Source

## 7.1. Interrupt Source

Each interrupt vector is independent and has its own priority.

|                                | Mask         | Priority | Interrupt Source                  | INT Vector Addr. |

|--------------------------------|--------------|----------|-----------------------------------|------------------|

|                                | Non-maskable | -        | RESET                             | 0000h            |

| Hardware<br>Interrupt maskable |              | 1        | INTO (External Interrupt 0)       | 0002h            |

|                                | maskable     | 2        | T0 (Timer0)                       | 0004h            |

|                                |              | 3        | VDI (Voltage Detection Indicator) | 0006h            |

|                                |              | 4        | WDT ( Watch-Dog Timer)            | 0008h            |

Table 7.1 Interrupt Source

### 7.2. Interrupt Control Register

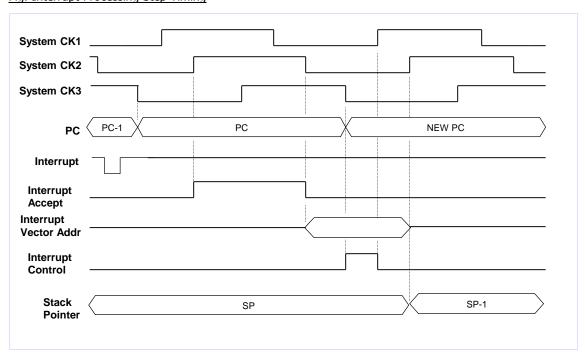

When interrupt is occurred, interrupt request flag is set,and Interrupt request is detected at the edge of interrupt signal. The accepted interrupt request flag is automatically cleared during interrupt cycle process. The interrupt request flag maintains ``1`` until the interrupt is accepted or is cleared in program. In reset state, interrupt request flag register (IRQR0) is cleared to ``0``.

It is possible to read the state of interrupt register and to manipulate the contents of register.

## • External Interrupt Edge selection Register 0 (IEDS0)

|               | 3 | 2 | 1     | 0     | _   |

|---------------|---|---|-------|-------|-----|

| IEDS0         | - | 1 | IED0H | IED0L | 16h |

| initial value | _ | - | 0     | 0     | -   |

| R/W           | W | W | W     | W     |     |

| Bit Name                                                                                       |    | Selection Mode                                |  |  |

|------------------------------------------------------------------------------------------------|----|-----------------------------------------------|--|--|

| -                                                                                              | -  | -                                             |  |  |

| _                                                                                              | -  | -                                             |  |  |

|                                                                                                | 00 | -                                             |  |  |

| IED0H                                                                                          | 01 | 01 Falling Edge Selection (1-to-0 transition) |  |  |

| IEDOL  10 Rising Edge Selection (0-to-1 transition)  11 Both Edge Selection (Falling & Rising) |    | INT0                                          |  |  |

|                                                                                                |    |                                               |  |  |

# • Interrupt Enable Register 0 (IENR0)

|               | 3    | 2    | 1   | 0     |     |

|---------------|------|------|-----|-------|-----|

| IENR0         | WDTE | VDIE | T0E | INT0E | 1Eh |

| initial value | 0    | 0    | 0   | 0     |     |

| R/W           | R/W  | R/W  | R/W | R/W   |     |

# Selection Mode of IENRO

| Bit Name |   | Selection Mode Re                   |  |  |  |

|----------|---|-------------------------------------|--|--|--|

| WDTE     | 1 | WDT Timer overflow Interrupt enable |  |  |  |

| VDIE     | 1 | oltage Detection Interrupt enable   |  |  |  |

| TOE      | 1 | mer0 Interrupt enable               |  |  |  |

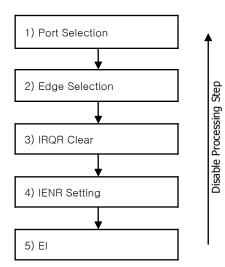

| INT0E    | 1 | External Interrupt 0 enable         |  |  |  |