# ABOV SEMICONDUCTOR Co., Ltd. 8-BIT MICROCONTROLLERS

# MC95FR332/432 MC95FR364/464

Data Sheet (Rev.2.0.1)

# **REVISION HISTORY**

#### **VERSION 0.0 (June 28, 2008)**

**Initial Version**

#### **VERSION 0.1 (November 27, 2008)**

- 1. Change OCD Ports from P1[1:0] to P2[2:1].

- 2. Change address of RMR(Remocon Mode Register) from BA<sub>H</sub> to E8<sub>H</sub>.

- 3. Fix the sequence of generating reset signal due to BOD when the device enters STOP mode and wakes up by an interrupt.

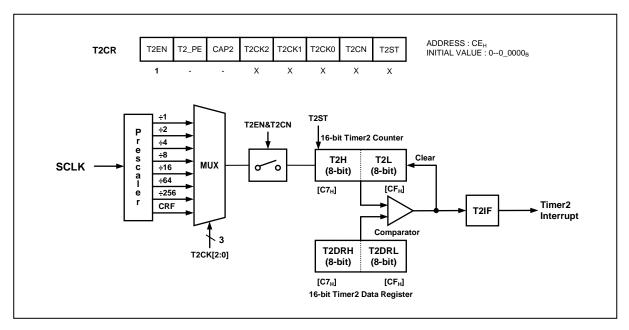

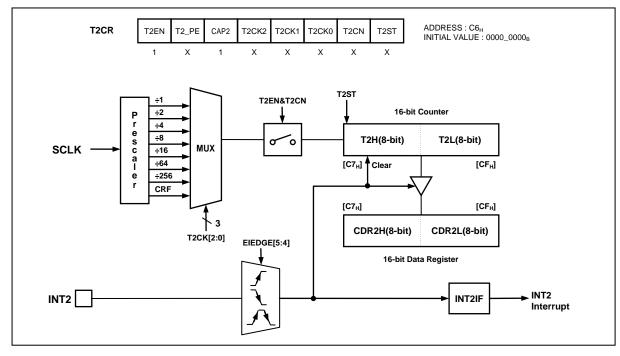

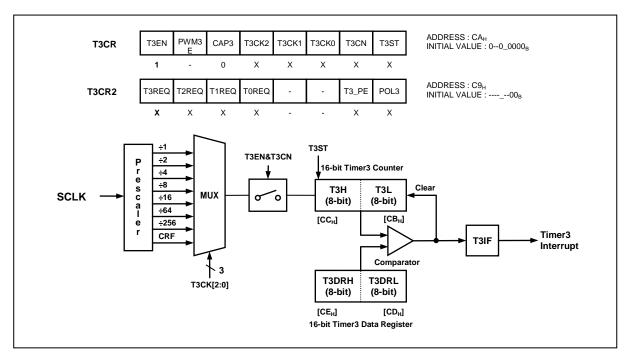

- 4. Append input capture function of timer 2, input capture function and pwm output function of timer 3.

#### **VERSION 0.1 (November 27, 2008)**

1. Correct the method of controlling REMOUT port.

#### **VERSION 0.3 (April 27, 2009)**

1. Fix BODOUT0/1/2/3/4 level.

BODOUT0: 1.70V (Typ.) ± 50mV

BODOUT1/2/3/4: 1.85, 1.95, 2.05, 2.15 (Typ.) ± 100mV

#### **VERSION 0.4 (May 25, 2009)**

- 1. Correct operating mode description.

- 2. Fix BODOUT1/2/3/4 level

BODOUT1/2/3/4: 1.75, 1.85, 1.95, 2.05 (Typ.) ± 100mV

#### **VERSION 0.5 (July 29, 2009)**

1. 1.2 Features: Endurance 10,000 times

2. 6. PORT STRUCTURE: Figure 6.1 & 6.2

3. BODOUT0 level: 1.65 ± 100mV

4. 7.6 DC CHARACTERISTICS

5. 10.6 Effective time of Interrupt Request : Figure 10.4

6. 10.7 Multiple Interrupts: Figure 10.5

7. 12.2 PERIPHERAL OPERATION IN SLEEP/STOP/BOD MODE: Table 12-1

8. Figure 12.2 Entry into BOD mode and Release sequence

9. 13.4 Noise Canceller for External Reset Pin: fix T<sub>RNC</sub> (2us → 8us)

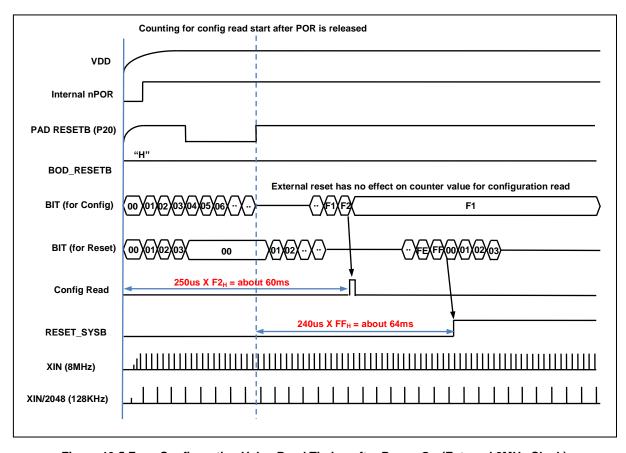

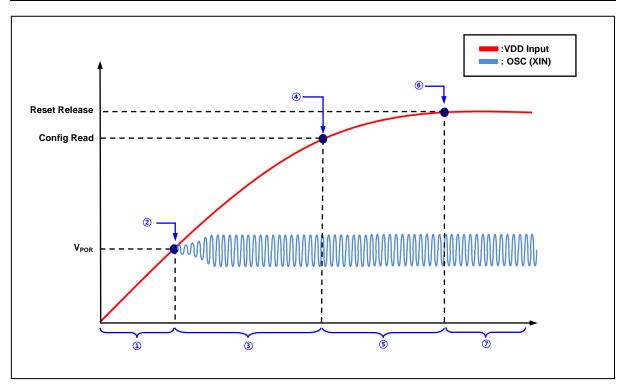

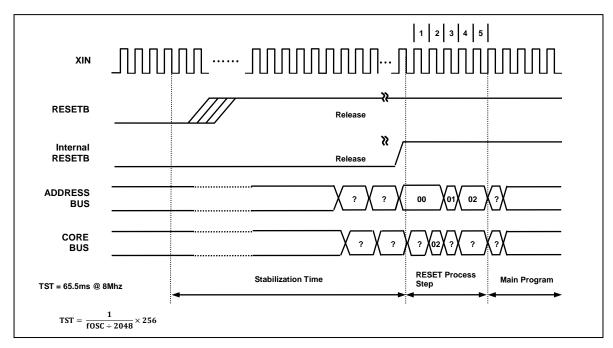

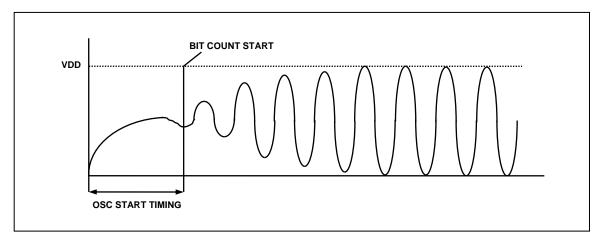

10. Figure 13.5 & 13.10: Fix config read time and reset release time

11. 15.5.3 : Fix function "void eeprom\_init(unsigned int addr)"

12. 16.1 FUSE Control Register

#### VERSION 0.6 (September 15, 2009)

1. 1.2 Features: remove WT

- 2. 12.0 POWER MANAGEMENT: Correct timing diagram in Figure 12.2~12.4.

- 3. Table 15-5 Memory protection using lock bit

- 4. Fix BODOUT0 in Table 7-4: 1.60V~1.75V

#### **VERSION 0.7 (November 5, 2009)**

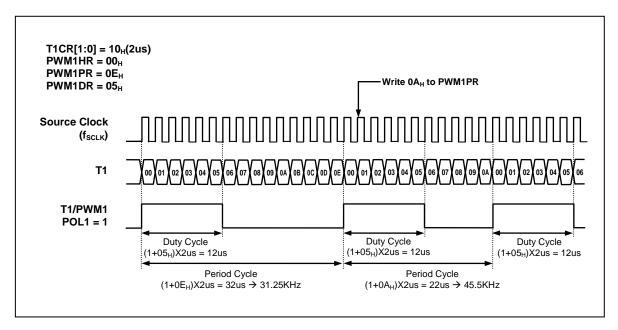

- 1. Fix POL0 to POL1 in Figure 11-14 & 11-15.

- 2. Fix POL0 to POL3 in Figure 11-18 through Figure 11-21.

- 3. Substitute figures in 4.PACKAGE DIMENSION.

- 4. Add features in 15.1.2. Features of FLASH/EEPROM.

- 5. Add "Caution" in FECR register description.

- 6. Add "7.9 REMOUT PORT CHARACTERISTICS".

- 7. Fix description of TXC flag in "11.7.8.2 Transmit flag and interrupt" and description of USTAT register in "11.7.12 Register Description".

- 8. Fix description of BODEN bit in BODR in "13.9 Register Description".

#### VERSION 0.8 (February 2, 2010)

1. Fix multi interrupt (Fig.10.5)

#### **VERSION 0.9 (February 26, 2010)**

- 1. Fix SFR map for RDRH, RDRL, CFRH and CFRL registers

- 2. Fix register name (RDC→CRC)

- 3. Add 28 TSSOP PKG

#### **VERSION 1.0 (March 8, 2010)**

- 1. Add pull-up resistor value @VDD=3.0V and VDD=2.4V in Table 7-6 DC Characteristics

- 2. Add 15.5.Data EEPROM program/erase

- 3. Fix mode entry sequence of Data EEPROM program/erase

#### **VERSION 1.1 (June 4, 2010)**

1. Add stop current consumption spec at room temperature in Table 7-6 DC Characteristics

# **VERSION 1.2 (February 8, 2011)**

- 1. Changed ABOV CI

- 2. Slightly modified description of PWM3 registers

- 3. Changed names of timer2/3 registers (ex. T3LDR→T3DRL)

#### **VERSION 2.0 (January 4, 2012)**

- 1. Correct open drain control register description(removed port 0 open drain control register)

- 2. Add Appendix B

- 3. Fix operating voltage range : 5.5V → 3.6V

Modify some C function code for safe operation in "15.5.2 Example of EEPROM control in C language"

Changed functions are "eeprom\_init() and eeprom\_mode\_exit()".

### **VERSION 2.0.1 (July 8, 2014)**

1. FUSE\_CONF register description is changed for more accurate explanation.

Version 2.0.1

Published by Design Team

©2012 ABOV Semiconductor Co., Ltd. All rights reserved.

Additional information of this manual may be served by ABOV Semiconductor offices in Korea or Distributors.

ABOV Semiconductor reserves the right to make changes to any information here in at any time without notice.

The information, diagrams and other data in this manual are correct and reliable; however, ABOV Semiconductor is in no way responsible for any violations of patents or other rights of the third party generated by the use of this manual.

# **Table of Contents**

| 1. OVERVIEW                                                         | 7  |

|---------------------------------------------------------------------|----|

| 1.1 Description                                                     | 7  |

| 1.2 Features                                                        | 7  |

| 1.3 Ordering Information                                            | 8  |

| 1.4 Development Tools                                               | 8  |

| 2. BLOCK DIAGRAM                                                    | 11 |

| 3. PIN CONFIGURATIONS                                               | 12 |

| 4. PACKAGE DIMENSION                                                | 15 |

| 5. PIN DESCRIPTION                                                  | 18 |

| 6. PORT STRUCTURES                                                  | 20 |

| 6.1 General Purpose I/O Port                                        | 20 |

| 6.2 External Interrupt I/O Port                                     | 21 |

| 7. ELECTRICAL CHARACTERISTICS                                       | 22 |

| 7.1 ABSOLUTE MAXIMUM RATINGS                                        | 22 |

| 7.2 RECOMMENDED OPERATING CONDITION                                 | 22 |

| 7.3 VOLTAGE DROPOUT CONVERTER(VDC) CHARACTERISTICS                  | 23 |

| 7.4 BROWN OUT DETECTOR(BOD) CHARACTERISTICS                         | 23 |

| 7.5 POWER-ON RESET CHARACTERISTICS                                  | 24 |

| 7.6 DC CHARACTERISTICS                                              | 24 |

| 7.7 AC CHARACTERISTICS                                              | 25 |

| 7.8 USART CHARACTERISTICS                                           | 26 |

| 7.9 REMOUT PORT CHARACTERISTICS                                     | 29 |

| 7.10 TYPICAL CHARACTERISTICS                                        | 30 |

| 8. MEMORY                                                           | 31 |

| 8.1 Program Memory                                                  | 31 |

| 8.2 IRAM                                                            | 32 |

| 8.3 XRAM                                                            | 35 |

| 8.4 Data EEPROM                                                     | 36 |

| 8.5 SFR map                                                         | 37 |

| 9. I/O PORTS                                                        | 40 |

| 9.1 Introduction.                                                   | 40 |

| 9.2 Register Description                                            | 40 |

| 10. INTERRUPT CONTROLLER                                            | 49 |

| 10.1 Overview                                                       | 49 |

| 10.2 External Interrupt                                             | 50 |

| 10.3 Block Diagram                                                  | 51 |

| 10.4 Interrupt Vectors                                              | 52 |

| 10.5 Interrupt Sequence                                             | 52 |

| 10.6 Effective time of Interrupt Request                            | 53 |

| 10.7 Multiple Interrupts                                            | 54 |

| 10.8 Interrupt Service Procedure                                    | 55 |

| 10.9 Generation of Branch Address to Interrupt Service Routine(ISR) | 55 |

| 10.10 Saving and Restoring General Purpose Registers                | 56 |

| 10.11 Interrupt Timing                                              | 57 |

| 10.12 Interrupt Registers                                           | 57 |

|                                                                     |    |

| 11. PERIPHERAL UNITS                             | 63  |

|--------------------------------------------------|-----|

| 11.1 Clock Generator                             | 63  |

| 11.2 Basic Interval Timer (BIT)                  | 65  |

| 11.3 Watch Dog Timer (WDT)                       | 68  |

| 11.4 TIMER/PWM                                   | 71  |

| 11.5 Carrier Generator                           | 97  |

| 11.6 Key Scan                                    | 104 |

| 11.7 USART                                       | 107 |

| 12. POWER MANAGEMENT                             | 125 |

| 12.1 Overview                                    | 125 |

| 12.2 PERIPHERAL OPERATION IN SLEEP/STOP/BOD MODE | 125 |

| 12.3 SLEEP mode                                  | 125 |

| 12.4 STOP mode                                   | 126 |

| 12.5 BOD mode                                    | 128 |

| 12.6 Register Map                                | 130 |

| 12.7 Register Description                        | 130 |

| 13. RESET                                        | 131 |

| 13.1 Overview                                    | 131 |

| 13.2 Reset source                                | 131 |

| 13.3 Block Diagram                               | 131 |

| 13.4 Noise Canceller for External Reset Pin      | 132 |

| 13.5 Power-On-RESET                              | 132 |

| 13.6 External RESETB Input                       | 135 |

| 13.7 Brown Out Detector                          | 136 |

| 13.8 Register Map                                | 137 |

| 13.9 Register Description                        | 137 |

| 14. ON-CHIP DEBUG SYSTEM                         | 139 |

| 14.1 Overview                                    | 139 |

| 14.2 Two-pin external interface                  | 140 |

| 15. FLASH/EEPROM CONTROLLER                      | 144 |

| 15.1 Overview                                    | 144 |

| 15.2 Register Map                                | 144 |

| 15.3 Register Description                        | 144 |

| 15.4 Memory map                                  | 148 |

| 15.5 Data EEPROM Program/Erase                   | 150 |

| 15.6 Security                                    | 155 |

| 15.7 FLASH/EEPROM operating mode                 | 157 |

| 16. ETC                                          | 158 |

| 16.1 FUSE Control Register                       | 158 |

| 17. APPENDIX                                     | 159 |

# MC95FR332/432/364/464

# **CMOS 8-bit Flash Microcontroller: UR**

#### 1. OVERVIEW

# 1.1 Description

The MC95FR332/432/364/464 is an advanced 8-bit microcontroller based on CMOS process with 32K/64K Bytes of Flash. This is powerful one which provides a highly flexible and cost effective solution to many embedded control applications.

The MC95FR332/432/364/464 provides the following features: 32K/64K Bytes of FLASH ROM<sup>NOTE1,</sup> NOTE2, 1024 Bytes of XRAM, 256 Bytes of IRAM, 8/16-bit Timer/Counter, WDT, 10-bit PWM, UASRT, Carrier Generator, 8-bit Basic Interval Timer, Watch Timer and Clock circuit. Also it provides one dedicated output pin which has large current drivability specialized for remote control application. Additionally, the MC95FR332/432/364/464 supports power saving modes to reduce power consumption.

$^{\mbox{\scriptsize NOTE1}}$  In this document, the ROM means non-volitile memory which is read-writable.

NOTE2 The MC95FR332/432/364/464 has a 32KB/64KB of non-volatile memory as ROM region, and user software in ROM can program or erase its contents assigned as data region. In general this kind of memory control is called "In Application Programming", IAP. In this document we'll distinguish FLASH between EEPROM. User software is stored in FLASH and data like table can be stored in EEPROM. Note that there's only one memory module in MC95FR332/432/364/464.

| Device Name   | FLASH size | IRAM | XRAM  | I/O PORT     | Package                         |

|---------------|------------|------|-------|--------------|---------------------------------|

| MC95FR332/432 | 32KB       | 256B | 1024B | 23 / 27 / 39 | 28 TSSOP, 28/32 SOP,<br>44 MQFP |

| MC95FR364/464 | 64KB       | 256B | 1024B | 23 / 27 / 39 | 28 TSSOP, 28/32 SOP,<br>44 MQFP |

#### 1.2 Features

• CPU

8-bit CISC Core (8051 Compatible, 2 clocks per cycle)

· 32K/64K Bytes On-chip FLASH

Endurance: 10,000 times Retention: 10 years

XRAM1024 Bytes

• IRAM 256 Bytes General Purpose I/O

23/27/39 Ports (P0[7:0],P1[7:0],P2[2:0],P3[7:0],P4[7:0],P5[3:0])

- One Basic Interval Timer

- Timer / Counter8-bit×2ch(16-bit×1ch) + 16-bit×2ch

- 16-bit PWM(Using Timer3)

- 10-bit PWM(Using Timer1)

- One Watch Dog Timer

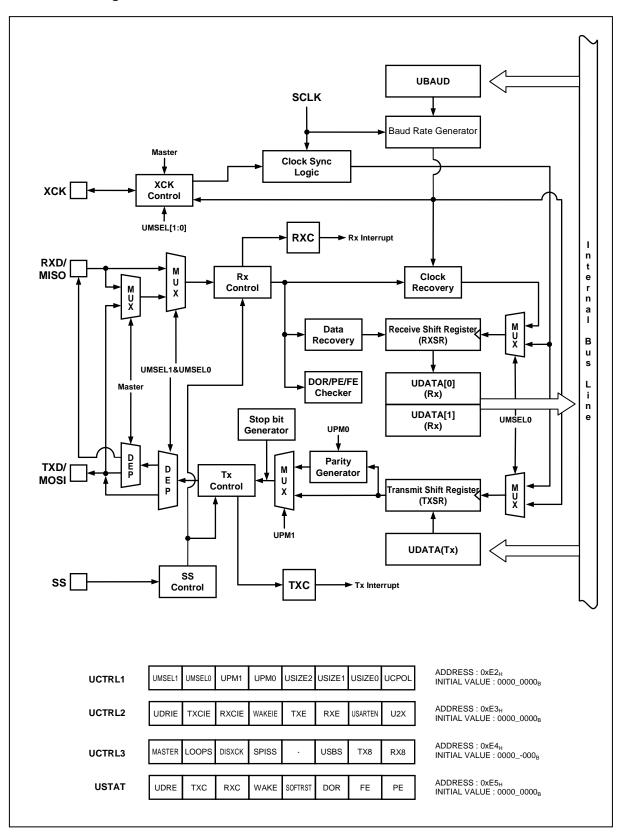

- One USART (or One SPI)

One Carrier Generator

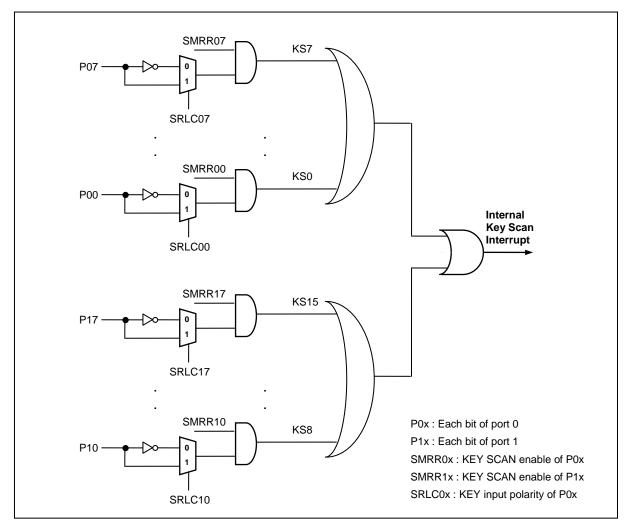

Key scan module P0[7:0], P1[7:0]

Interrupt Sources

External: 4

Pin Change Interrupt(P0): 1 USART or SPI (Rx/Tx): 2

Key scan: 1

Carrier Generator: 1

WDT : 1 BIT : 1

Timer0,1,2,3 : 4 EEPROM : 1

· Power On Reset

- · Programmable Brown-Out Detector

- Minimum Instruction Execution Time

200ns (@10MHz, 1 Cycle NOP Instruction)

- Power down mode

SLEEP, STOP mode

- Operating Frequency

1 ~ 10MHz

Operating Voltage

1.75V ~ 3.6V (@ 1 ~ 10MHz)

Operating Temperature

-40 ~ +85°C

PKG Type

28 TSSOP, 28/32 SOP, 44 MQFP Available Pb free package

#### 1.3 Ordering Information

| Device name | ROM size   | IRAM size | XRAM size | Package  |

|-------------|------------|-----------|-----------|----------|

| MC95FR332R  | 32KB FLASH |           |           | 28 TSSOP |

| MC95FR332M  |            | 256B      | 1024B     | 28 SOP   |

| MC95FR332D  |            | 230B      | 10246     | 32 SOP   |

| MC95FR432Q  |            |           |           | 44 MQFP  |

| MC95FR364R  | 64KB FLASH | 256B      |           | 28 TSSOP |

| MC95FR364M  |            |           | 1024B     | 28 SOP   |

| MC95FR364D  |            |           | 10246     | 32 SOP   |

| MC95FR464Q  |            |           |           | 44 MQFP  |

**Table 1-1 Ordering Information**

#### 1.4 Development Tools

#### 1.4.1 Compiler

ABOV semiconductor does not provide any compiler for MC95FR332/432/364/464. As the CPU core of MC95FR332/432/364/464 is Mentor 8051, you can use all kinds of third party's standard 8051 compiler.

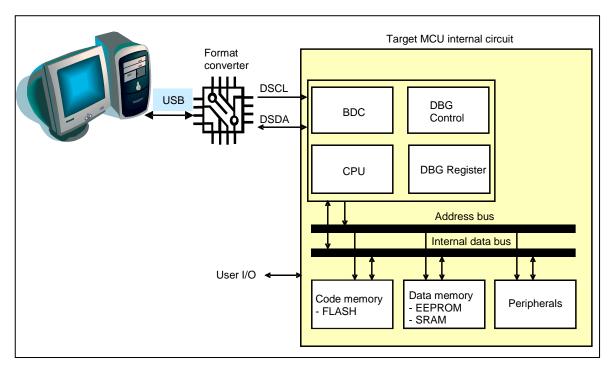

#### 1.4.2 OCD emulator and debugger

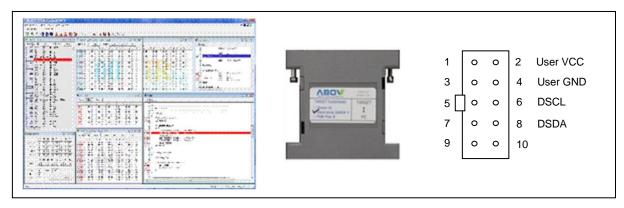

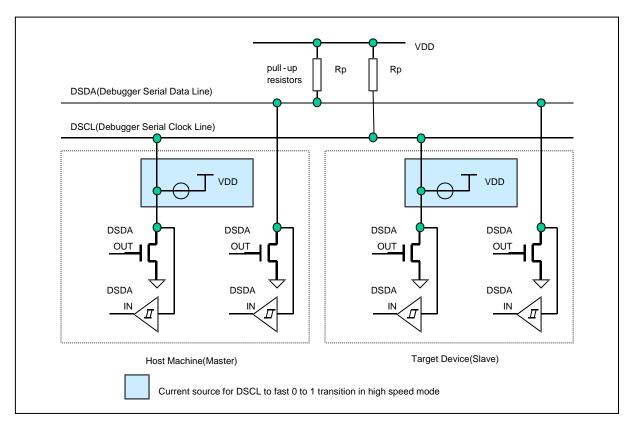

OCD(On Chip Debugger) program is a debugging software for ABOV semiconductor's 8051 MCU series. OCD uses only two lines to download a user code, to read and modify the internal memory or SFR(Special Function Register)s. And also OCD controls MCU's internal debugging logic, which means OCD controls emulation, step run, monitoring, etc.

OCD debugger program works on Microsoft-Windows NT, 2000, XP, Vista(32-bit) operating system.

If you want to see details more, please refer to OCD debugger manual. You can download debugger S/W and manual from out web-site.

The connecting pins between PC and MCU is as follows:

- DSCL (P2[1] of MC95FR332/432/364/464)

- DSDA (P2[2] of MC95FR332/432/364/464)

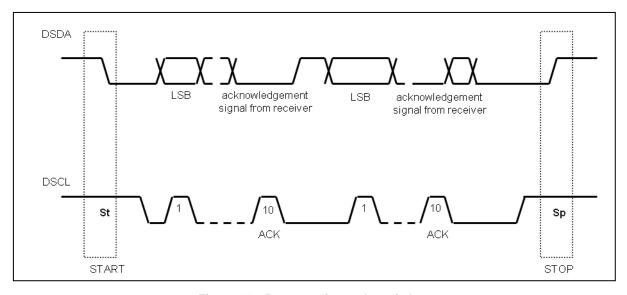

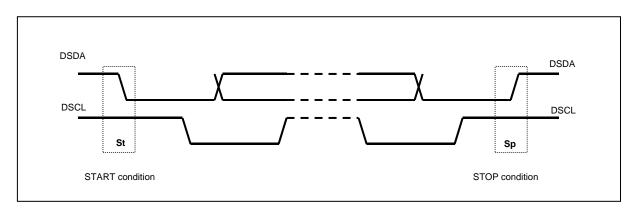

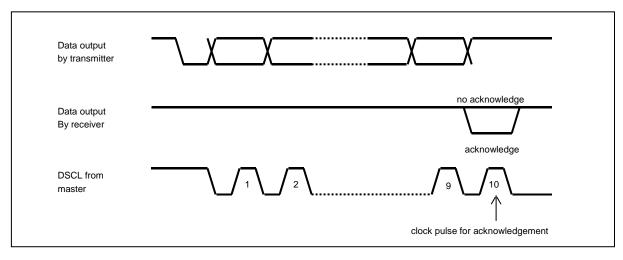

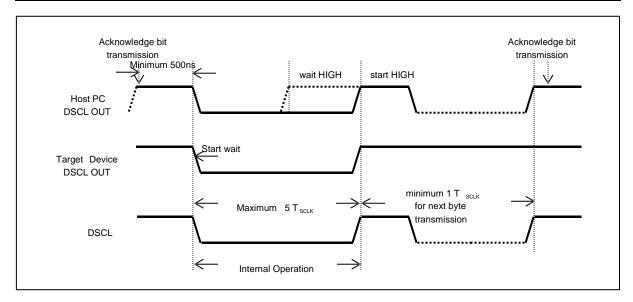

Figure 1.1 OCD Software and Connector

#### 1.4.3 Programmer

To program or download user code into the ROM of MC95FR332/432/364/464, ABOV semiconductor provides several tools. As a single programmer which can program only one chip at a time, there are PGMPlus for parallel programming and ISP/OCD for serial programming and debugging. On the other hand, you can program multi-chips at a time by using a gang programmer. Gang programmer can program up to 8 devices simultaneously.

### 1.4.3.1 Single programmer

1. PGMplus USB: This is a parallel programmer which is smaller and faster than our previous parallel programmer PGM Plus III.

Figure 1.2 PGMplus USB

2. Ez-ISP: This is one of stand alone type ISP tool. Notable thing is that it provides power to the target MCU.

Figure 1.3 Ez-ISP

3. OCD emulator: You can program or debug the MCU via OCD. Because the OCD suports ISP(In System Programming), it does not require additional H/W except for developer's target system.

# 1.4.3.2 Gang programmer

The gang programmer can program maximum 8 MCUs at a time. So it is mainly used in mass production line. As gang programmer is standalone type, it does not require host PC.

Figure 1.4 Gang programmer

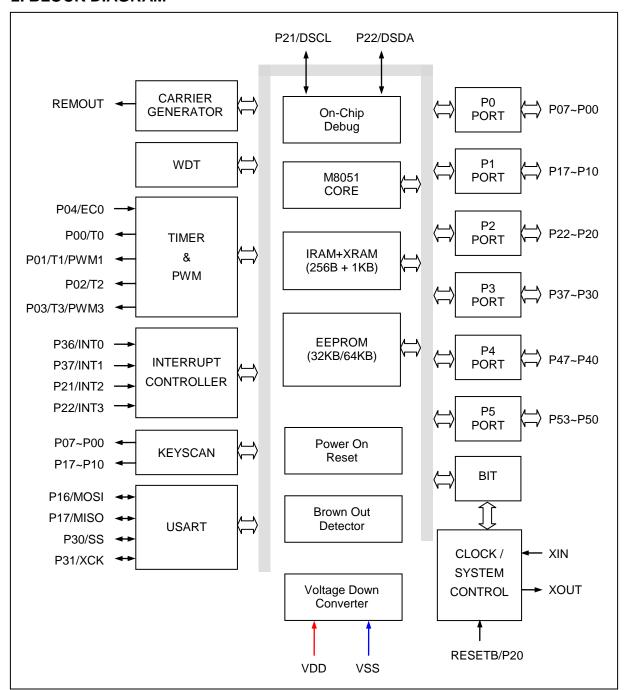

#### 2. BLOCK DIAGRAM

Figure 2.1 Block Diagram of MC95FR332/432/364/464

| PIN | Туре | Option | Remarks      |

|-----|------|--------|--------------|

| P20 | I/O  | RESETB | FUSE Control |

#### 3. PIN CONFIGURATIONS

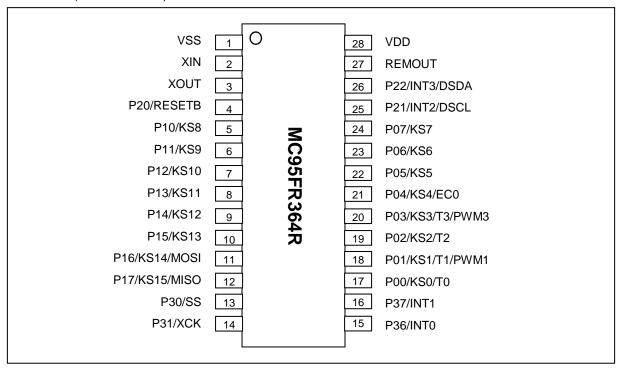

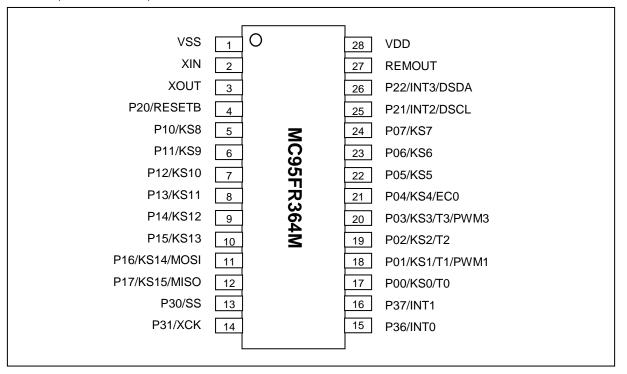

28 TSSOP (MC95FR364R)

Figure 3.1 28 TSSOP Pinout (MC95FR364R)

#### 28 SOP (MC95FR364M)

Figure 3.2 28 SOP Pinout (MC95FR364M)

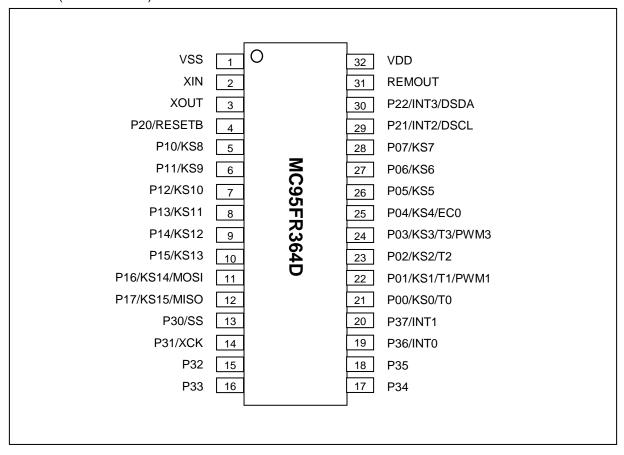

#### 32 SOP (MC95FR364D)

Figure 3.3 32 SOP Pinout (MC95FR364D)

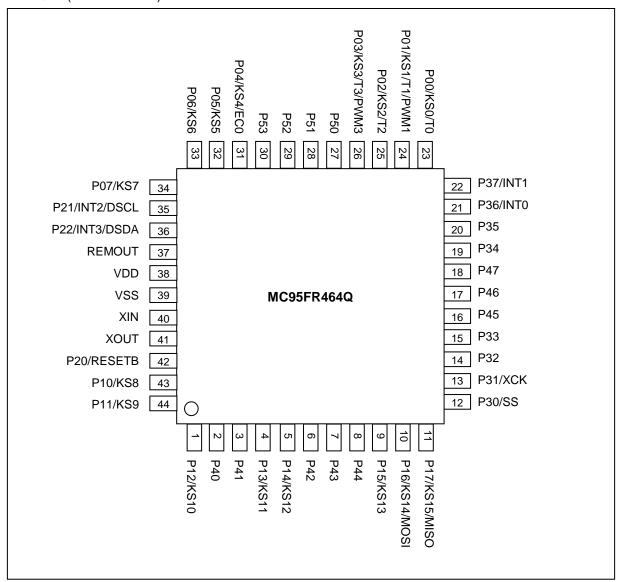

# 44 MQFP (MC95FR464Q)

Figure 3.4 44 MQFP Pinout (MC95FR464Q)

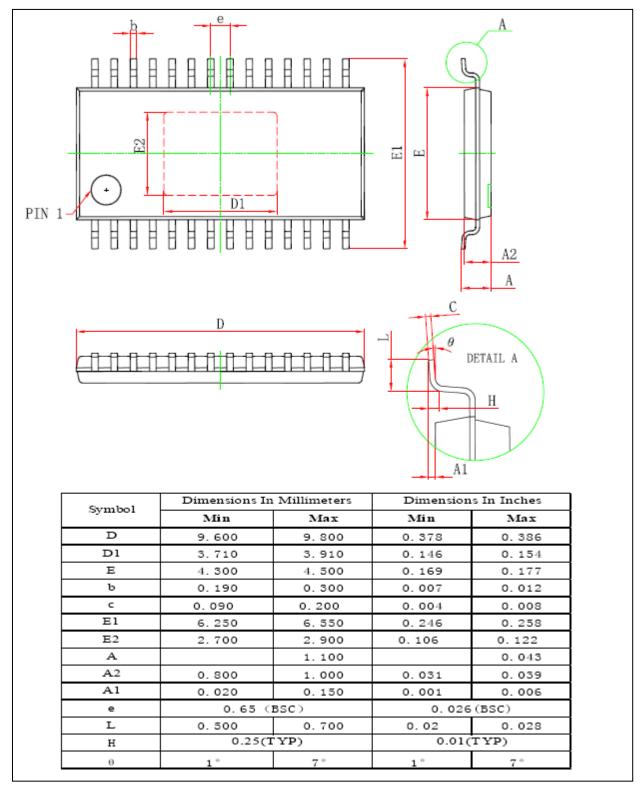

#### 4. PACKAGE DIMENSION

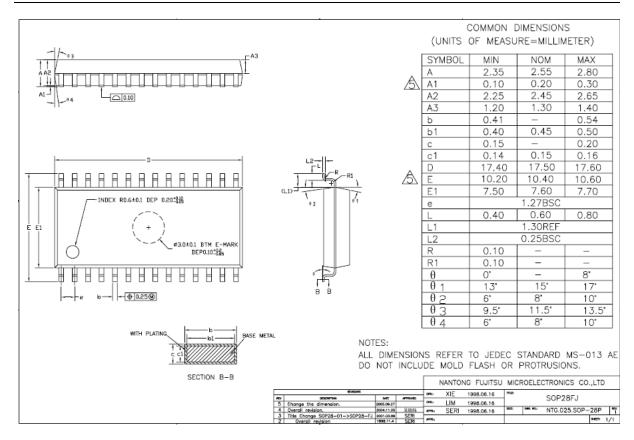

Figure 4.1 PKG DIMENSION (28 TSSOP)

Figure 4.2 PKG DIMENSION (28 SOP)

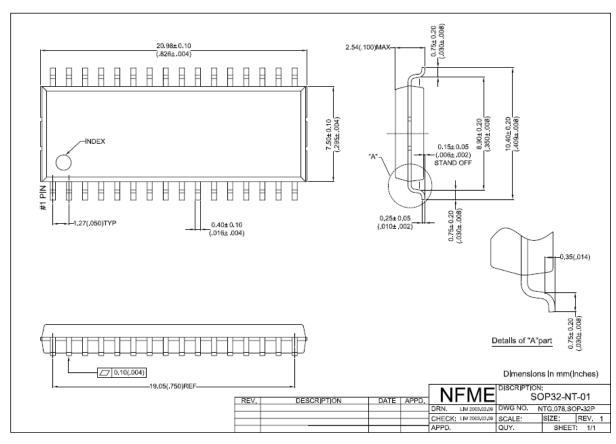

Figure 4.3 PKG DIMENSION (32 SOP)

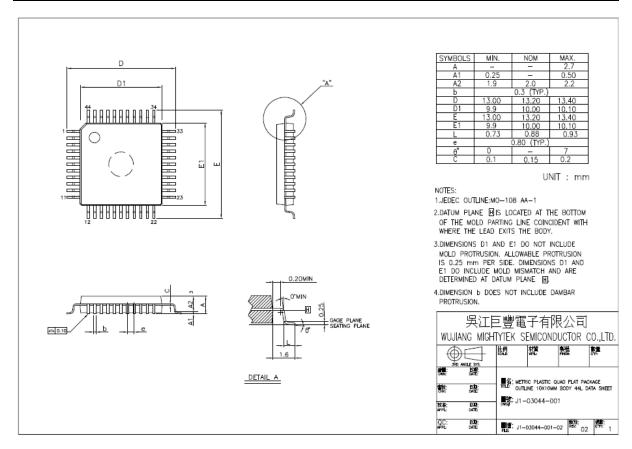

Figure 4.4 PKG DIMENSION (44 MQFP)

# **5. PIN DESCRIPTION**

18

| PIN<br>Name | I/O | Function                                                                                                             | @RESET | Shared with |

|-------------|-----|----------------------------------------------------------------------------------------------------------------------|--------|-------------|

| P00         | I/O | - 8-bit I/O port, P0.                                                                                                | Input  | KS0/T0      |

| P01         |     | - Can be set in input or output mode bitwise.                                                                        |        | KS1/T1/PWM1 |

| P02         |     | <ul> <li>Internal pull-up resistor can be activated by<br/>setting PxnPU bit in PxPU register when this</li> </ul>   |        | KS2/T2      |

| P03         |     | port is used as input port.                                                                                          |        | KS3/T3/PWM3 |

| P04         | =   | - Can be configured as an open drain output mode by setting PxnOD bit in PxOD register.                              |        | KS4/EC0     |

| P05         |     |                                                                                                                      |        | KS5         |

| P06         |     |                                                                                                                      |        | KS6         |

| P07         |     |                                                                                                                      |        | KS7         |

| P10         | I/O | 8-bit I/O port, P1.                                                                                                  | Input  | KS8         |

| P11         |     | - Can be set in input or output mode bitwise.                                                                        |        | KS9         |

| P12         | =   | <ul> <li>Internal pull-up resistor can be activated by<br/>setting PxnPU bit in PxPU register when this</li> </ul>   |        | KS10        |

| P13         |     | port is used as input port.                                                                                          |        | KS11        |

| P14         | =   | - Can be configured as an open drain output mode by setting PxnOD bit in PxOD register.                              |        | KS12        |

| P15         | =   |                                                                                                                      |        | KS13        |

| P16         | =   |                                                                                                                      |        | KS14/MOSI   |

| P17         |     |                                                                                                                      |        | KS15/MISO   |

| P20         | I/O | - 3-bit I/O port, P2.                                                                                                | Input  | RESETB NOTE |

| P21         |     | - Can be set in input or output mode bitwise.                                                                        |        | INT2/DSCL   |

| P22         |     | <ul> <li>Internal pull-up resistor can be activated by<br/>setting PxnPU bit in PxPU register when this</li> </ul>   |        | INT3/DSDA   |

| -           | -   | port is used as input port.  - Can be configured as an open drain output mode by setting PxnOD bit in PxOD register. |        | -           |

NOTE When P20 is used as a external reset pin(=RESETB) by the FUSE configuration, this pin is configured as an input port with internal pull-up resistor on.

| PIN<br>Name | I/O | Function                                                                                     | @RESET | Shared with |

|-------------|-----|----------------------------------------------------------------------------------------------|--------|-------------|

| P30         | I/O | - 8-bit I/O port, P3.                                                                        | Input  | SS          |

| P31         |     | - Can be set in input or output mode bitwise.                                                |        | XCK         |

| P32         |     | - Internal pull-up resistor can be activated by setting PxnPU bit in PxPU register when this |        | -           |

| P33         |     | port is used as input port.                                                                  |        | -           |

| P34         |     | - Can be configured as an open drain output mode by setting PxnOD bit in PxOD register.      |        | -           |

| P35         |     |                                                                                              |        | -           |

| P36         |     |                                                                                              |        | INT0        |

| P37         |     |                                                                                              |        | INT1        |

| P40         | I/O | - 8-bit I/O port, P4                                                                         | Input  | -           |

| P41         |     | - Can be set in input or output mode bitwise.                                                |        | -           |

| P42         |     | - Internal pull-up resistor can be activated by setting PxnPU bit in PxPU register when this |        | -           |

| P43         |     | port is used as input port.                                                                  |        | -           |

| P44         |     | - Can be configured as an open drain output mode by setting PxnOD bit in PxOD register.      |        | -           |

| P45         |     |                                                                                              |        | -           |

| P46         |     |                                                                                              |        | -           |

| P47         |     |                                                                                              |        | -           |

| P50         | I/O | - 4-bit I/O port, P5                                                                         | Input  | -           |

| P51         |     | - Can be set in input or output mode bitwise.                                                |        | -           |

| P52         |     | - Internal pull-up resistor can be activated by setting PxnPU bit in PxPU register when this |        | -           |

| P53         |     | port is used as input port.                                                                  |        | -           |

| -           | -   | - Can be configured as an open drain output mode by setting PxnOD bit in PxOD register.      |        | -           |

| XIN         | I   | Oscillator input                                                                             |        | -           |

| XOUT        | 0   | Oscillator output                                                                            |        | -           |

| REMOUT      | 0   | Push-pull high current output                                                                |        | -           |

# **6. PORT STRUCTURES**

# 6.1 General Purpose I/O Port

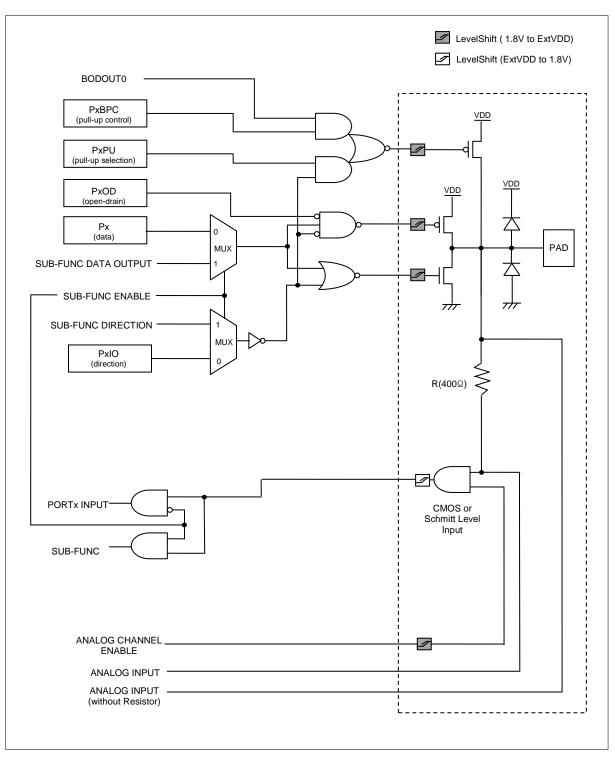

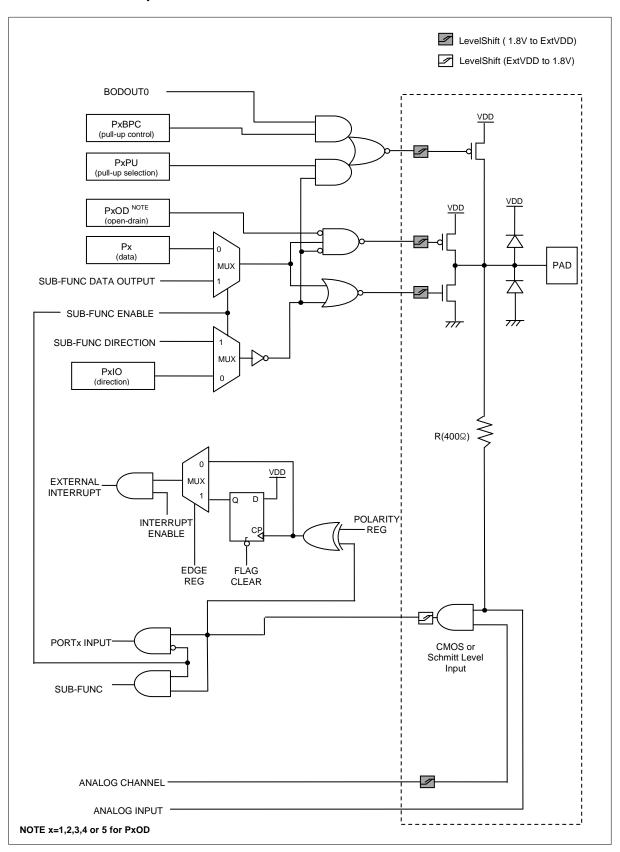

Figure 6.1 General I/O

# 6.2 External Interrupt I/O Port

Figure 6.2 I/O with external interrupt function

# 7. ELECTRICAL CHARACTERISTICS

#### 7.1 ABSOLUTE MAXIMUM RATINGS

| Parameter               | Symbol | Rating       | Unit |

|-------------------------|--------|--------------|------|

| Complex Voltages        | VDD    | -0.3~+4.2    | V    |

| Supply Voltage          | VSS    | -0.3~+0.3    | V    |

|                         | VI     | -0.3~VDD+0.3 | V    |

|                         | VO     | -0.3~VDD+0.3 | V    |

| N 1976 B:               | IOH    | 10           | mA   |

| Normal Voltage Pin      | ΣΙΟΗ   | 80           | mA   |

|                         | IOL    | 20           | mA   |

|                         | ΣIOL   | 160          | mA   |

| Total Power Dissipation | PT     | 600          | mW   |

| Storage Temperature     | TSTG   | -65~+150     | °C   |

**Table 7-1 Absolute Maximum Ratings**

#### 7.2 RECOMMENDED OPERATING CONDITION

| Parameter             | Symbol | Condition                   | MIN | TYP | MAX | Unit |

|-----------------------|--------|-----------------------------|-----|-----|-----|------|

| Supply Voltage        | VDD    | f <sub>XIN</sub> =1.0~10MHz | 1.8 | 1   | 3.6 | V    |

| Operating Temperature | TOPR   | VDD=1.65~3.6V               | -40 | -   | 85  | °C   |

| Operating Frequency   | FOPR   | f <sub>XIN</sub>            | 1   | -   | 10  | MHz  |

**Table 7-2 Recommended Operating Condition**

NOTE Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliablility.

# 7.3 VOLTAGE DROPOUT CONVERTER(VDC) CHARACTERISTICS

| Parameter             | Symbol | Condition   | MIN  | TYP | MAX  | Unit       |

|-----------------------|--------|-------------|------|-----|------|------------|

| Operating Voltage     |        | -           | 1.62 | -   | 4.00 | V          |

| Operating Temperature |        | -           | -40  | -   | +85  | $^{\circ}$ |

| Regulation Voltage    |        | -           | 1.62 | 1.8 | 1.98 | V          |

| Drop-out Voltage      |        | -           | -    | -   | 0.02 | V          |

| O mark British III    |        | RUN         | -    | 10  | -    | mA         |

| Current Drivability   |        | STOP        | -    | 10  | -    | uA         |

|                       | IDD    | RUN         | -    | -   | 1    | mA         |

| Operating Current     | SIDD   | STOP        | -    | -   | 1    | uA         |

| Mode Transition Time  | TRAN   | STOP to RUN | -    | -   | 200  | us         |

**Table 7-3 Voltage Dropout Converter Characteristics**

**RUN** When the MC95FR332/432/364/464 is in normal operating mode, the VDC should provide enough current to the entire chip. So, in this mode of operating condition, the VDC is set to "RUN" mode to accommodate MCU's normal RUN mode.

**STOP** When the MC95FR332/432/364/464 enters STOP mode to save current consumption, all internal logics stop operation including x-tal oscillator . In this mode, the MC95FR332/432/364/464 makes the VDC to enter "STOP" mode , leading to least current consumption mode.

# 7.4 BROWN OUT DETECTOR(BOD) CHARACTERISTICS

| Parameter             | Symbol  | Condition | MIN  | TYP  | MAX  | Unit |

|-----------------------|---------|-----------|------|------|------|------|

| Operating Voltage     |         | -         | 1.5  | -    | 4.00 | V    |

| Operating Temperature |         | -         | -40  | -    | +85  | °C   |

|                       | BODOUT0 | NOTE      | 1.60 | 1.65 | 1.75 | V    |

|                       | BODOUT1 | NOTE      | 1.65 | 1.75 | 1.85 | V    |

| Detection Level       | BODOUT2 | NOTE      | 1.75 | 1.85 | 1.95 | V    |

|                       | BODOUT3 | NOTE      | 1.85 | 1.95 | 2.05 | V    |

|                       | BODOUT4 | NOTE      | 1.95 | 2.05 | 2.15 | V    |

|                       | IDD     | -         | -    | -    | 50   | uA   |

| Operating Current     | SIDD    | -         | -    | -    | 1    | uA   |

**Table 7-4 Brown Out Detector Characteristics**

NOTE BODOUT0 is a voltage level or flag indicating it can generate internal reset due to voltage drop. When the external power drops below the BODOUT0 voltage level, the BOD detects the power condition and makes the device enter STOP-like mode called BOD mode. When the external power is restored, a BOD reset is generated according to pre-defined sequence and the device is initialized. BODOUT1/2/3/4 also indicate voltage level or flag. When the external power drops below the level indicated in abov table, the associated flag is set to '1' and these values can be read through the BODSR register. These flags may be used to check the battery status.

NOTE The operating modes of VDC itself are as follows.

# 7.5 POWER-ON RESET CHARACTERISTICS

| Parameter             | Symbol | Condition | MIN | TYP | MAX | Unit |

|-----------------------|--------|-----------|-----|-----|-----|------|

| Operating Voltage     |        | -         | -   | -   | 3.6 | V    |

| Operating Temperature |        | -         | -40 | -   | +85 | °C   |

| RESET Release Level   |        | -         | 1.3 | 1.4 | 1.5 | V    |

|                       | IDD    | -         | -   | -   | 10  | uA   |

| Operating Current     | SIDD   | -         | -   | -   | 1   | uA   |

**Table 7-5 Power-On Reset Characteristics**

# 7.6 DC CHARACTERISTICS

(VDD =1.8~3.6V, VSS =0V,  $f_{XIN}$ =10.0MHz, TA=-40~+85  $^{\circ}$ C)

| Parameter                     | Symbol | Condition                                   | MIN    | TYP | MAX     | Unit |

|-------------------------------|--------|---------------------------------------------|--------|-----|---------|------|

| t \/- t                       | VIL1   | P0,P1,P20 (Schmitt Trigger Input)           | -0.5   | -   | 0.2VDD  | V    |

| Input Low Voltage             | VIL2   | P2[2:1],P3,P4,P5 (Normal Input)             | -0.5   | -   | 0.2VDD  | V    |

| Input High                    | VIH1   | P0,P1,P20 (Schmitt Trigger Input)           | 0.8VDD | -   | VDD+0.5 | V    |

| Voltage                       | VIH2   | P2[2:1],P3,P4,P5 (Normal Input)             | 0.7VDD | -   | VDD+0.5 | V    |

| Output Low<br>Voltage         | VOL1   | P0,P1,P2,P3,P4,P5<br>(IOL=10mA, VDD=3.0V)   | -      | -   | 1       | V    |

| Output High<br>Voltage        | VOH1   | P0,P1,P2,P3,P4,P5<br>(IOH=-4.0mA, VDD=3.0V) | 3.5    | -   | -       | V    |

| Input High<br>Leakage Current | IIH    | P0,P1,P2,P3,P4,P5                           |        |     | 1       | uA   |

| Input Low<br>Leakage Current  | IIL    | P0,P1,P2,P3,P4,P5                           | -1     |     |         | uA   |

|                               | RPU1   | P0,P1,P2,P3,P4,P5                           | 00     | 85  | 110     | kΩ   |

|                               |        | (VDD=3.0V, TA=+25℃)                         | 60     |     |         |      |

|                               | RPU2   | P0,P1,P2,P3,P4,P5                           |        | 145 | 170     | kΩ   |

|                               |        | (VDD=2.4V, TA=+25°C)                        | 80     |     |         |      |

| Power Supply<br>Current       | IDD1   | RUN Mode, f <sub>XIN</sub> =10MHz@3.6V      | -      | -   | 15      | mA   |

|                               | IDD2   | SLEEP Mode, f <sub>XIN</sub> =10MHz@3.6V    | -      | 1   | 12      | mA   |

|                               | IDD3   | STOP Mode @3.6V                             | -      | -   | 10      | uA   |

|                               | IDD4   | STOP Mode @3.0V (TA=25℃)                    |        | 2   | 5       | uA   |

**Table 7-6 DC Characteristics**

# 7.7 AC CHARACTERISTICS

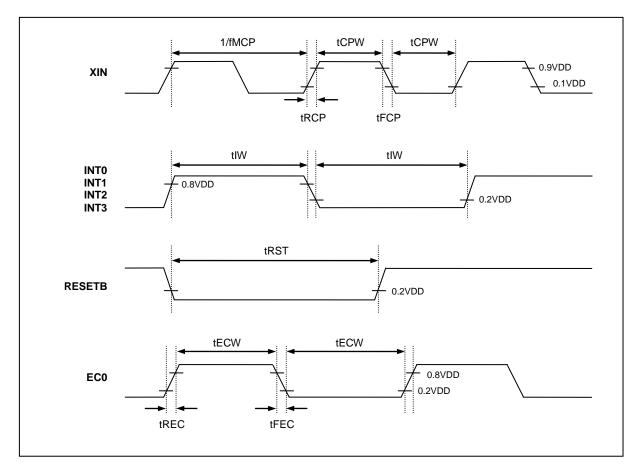

| Parameter                                     | Symbol    | PIN       | MIN | TYP | MAX  | Unit |

|-----------------------------------------------|-----------|-----------|-----|-----|------|------|

| Operating Frequency                           | fMCP      | XIN       | 1   | -   | 10   | MHz  |

| System Clock Cycle Time                       | tSYS      | -         | 100 | -   | 1000 | ns   |

| Oscillation Stabilization Time (8MHz)         | tMST1     | XIN, XOUT | -   | -   | 10   | ms   |

| External Clock "H" or "L" Pulse Width         | tCPW      | XIN       | 90  | -   | -    | ns   |

| External Clock Transition Time                | tRCP,tFCP | XIN       | -   | -   | 10   | ns   |

| Interrupt Input Width                         | tIVV      | INT0~INT3 | 2   | -   | -    | tSYS |

| RESETB Input Pulse "L" Width                  | tRST      | RESETB    | -   | 8   | -    | us   |

| External Counter Input "H" or "L" Pulse Width | tECW      | EC0       | 2   | _   | -    | tSYS |

| Event Counter Transition Time                 | tREC,tFEC | EC0       | -   | -   | 20   | ns   |

**Table 7-7 AC Characteristics**

Figure 7.1 AC Timing

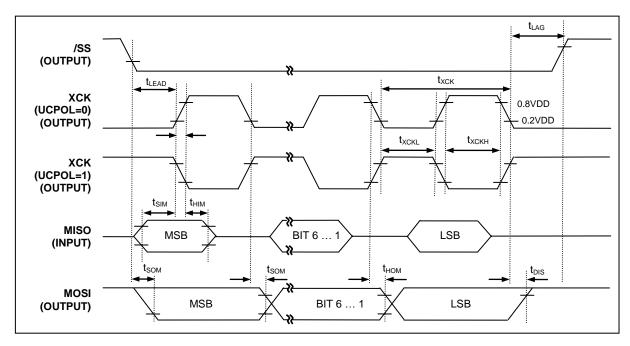

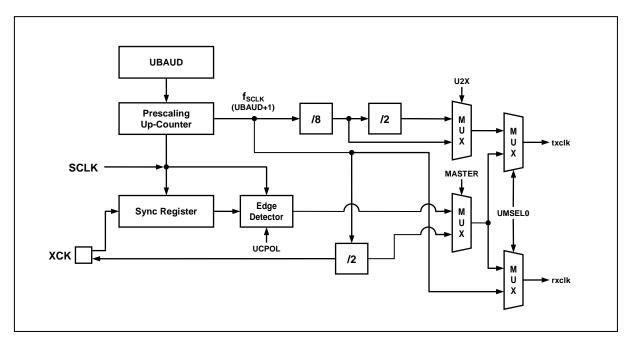

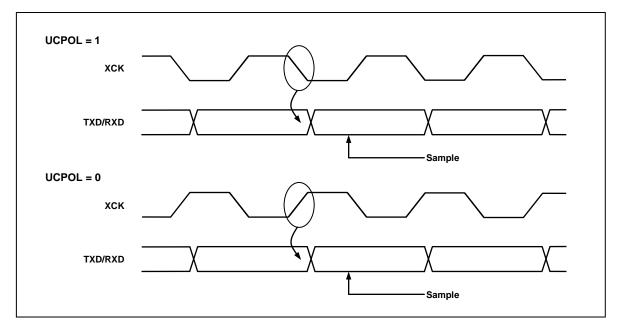

#### 7.8 USART CHARACTERISTICS

The following table and figure show the timing codition of USART in SPI or Synchronous mode of operation. The usart is one of peripherals in MC95FR332/432/364/464.  $^{NOTE1}$ .

(VDD =3.0V±10%, VSS =0V, TA=-40~+85°C)

| Parameter                 |        | Symbol <sup>NOTE2</sup> | MIN                  | MAX                  | Unit              |

|---------------------------|--------|-------------------------|----------------------|----------------------|-------------------|

| System clock period       |        | t <sub>SCLK</sub>       | 100                  | 1000                 | ns                |

| Clock (XCK) period        |        | t <sub>XCK</sub>        | 4                    | 1028                 | t <sub>SCLK</sub> |

| Clock (XCK) high time     |        | t <sub>XCKH</sub>       | 2                    | 514                  | t <sub>SCLK</sub> |

| Clock (XCK) low time      |        | $t_{XCKL}$              | 2                    | 514                  | t <sub>SCLK</sub> |

| Lead time                 |        |                         |                      |                      |                   |

|                           | Master | $t_{\sf LEAD}$          | 0.5 t <sub>XCK</sub> | 0.5 t <sub>XCK</sub> | ns                |

|                           | Slave  | $t_{\sf LEAD}$          | 2 t <sub>SCLK</sub>  | -                    |                   |

| Lag time                  |        |                         |                      |                      |                   |

|                           | Master | $t_LAG$                 | 0.5 t <sub>XCK</sub> | 0.5 t <sub>XCK</sub> | ns                |

|                           | Slave  | $t_LAG$                 | 2 t <sub>SCLK</sub>  | -                    |                   |

| Data setup time (inputs)  |        |                         |                      |                      |                   |

|                           | Master | t <sub>SIM</sub>        | 2                    | 2                    | t <sub>SCLK</sub> |

|                           | Slave  | t <sub>SIS</sub>        | 2                    | 2                    |                   |

| Data hold time (inputs)   |        |                         |                      |                      |                   |

|                           | Master | t <sub>HIM</sub>        | 10                   | -                    | ns                |

|                           | Slave  | t <sub>HIS</sub>        | 10                   | -                    |                   |

| Data setup time (outputs) |        |                         |                      |                      |                   |

|                           | Master | t <sub>SOM</sub>        | 2                    | 2                    | t <sub>SCLK</sub> |

|                           | Slave  | t <sub>SOS</sub>        | 2                    | 2                    |                   |

| Data hold time (outputs)  |        |                         |                      |                      |                   |

|                           | Master | t <sub>HOM</sub>        | -10                  | -                    | ns                |

|                           | Slave  | t <sub>HOS</sub>        | -10                  | -                    |                   |

| Disable time              |        | t <sub>DIS</sub>        | 1                    | 2                    | t <sub>SCLK</sub> |

Table 7-8 Timing characteristics of USART in SYNC. or SPI mode of operations

NOTE1 In synchronous mode, Lead and Lag time with respect to SS pin is ignored. And the case of UCPHA=0 is also applied to SPI mode only.

$<sup>^{\</sup>rm NOTE2}$  All timing is shown with respect to 20% VDD and 80% VDD.

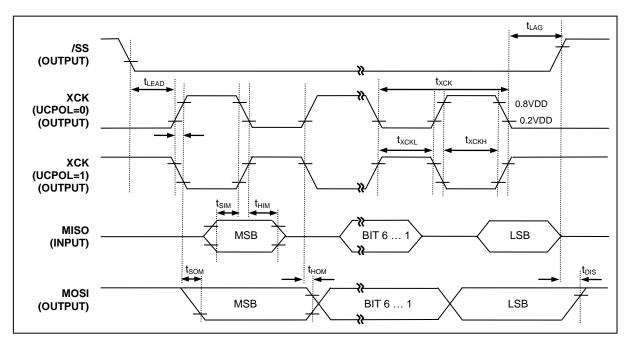

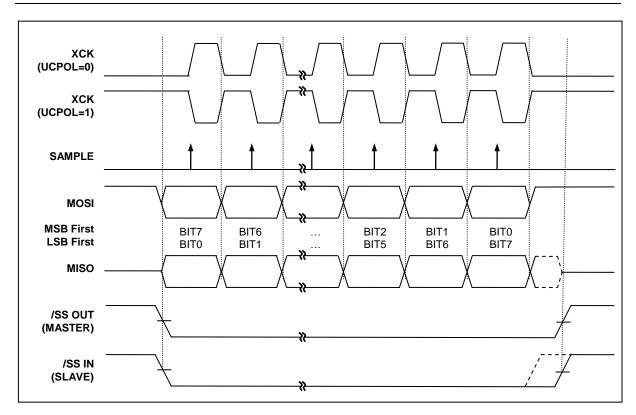

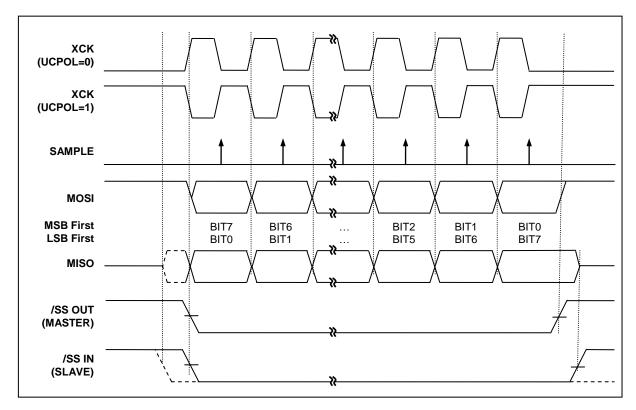

Figure 7.2 SPI master mode timing (UCPHA = 0, MSB first)

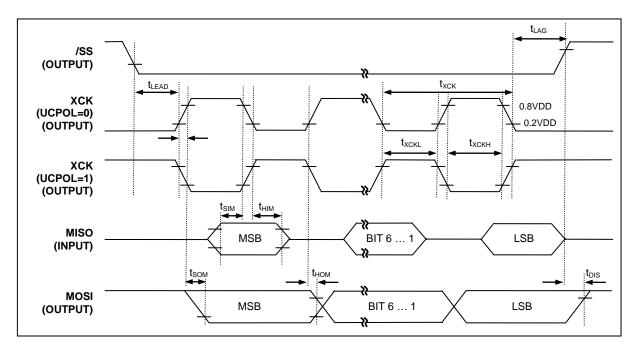

Figure 7.3 SPI / Synchronous master mode timing (UCPHA = 1, MSB first)

<sup>NOTE</sup> When in Synchronous mode, the START bit becomes MSB and the 1<sup>st</sup> or 2<sup>nd</sup> STOP bit becomes LSB.

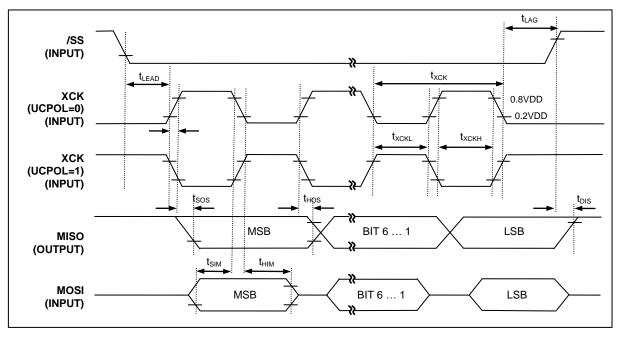

Figure 7.4 SPI slave mode timing (UCPHA = 0, MSB first)

Figure 7.5 SPI / Synchronous slave mode timing (UCPHA = 1, MSB first)

NOTE When in Synchronous mode, the START bit becomes MSB and the 1<sup>st</sup> or 2<sup>nd</sup> STOP bit becomes LSB.

# 7.9 REMOUT PORT CHARACTERISTICS

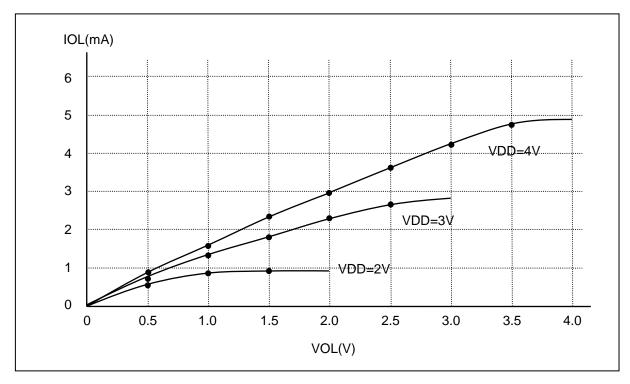

Figure 7.6 IOL vs VOL

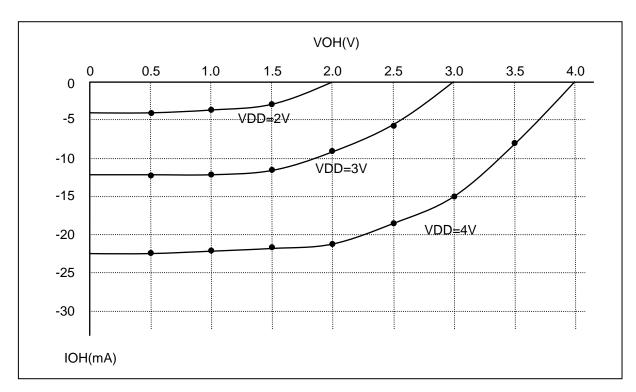

Figure 7.7 IOH vs VOH

#### 7.10 TYPICAL CHARACTERISTICS

These graphs and tables provided in this section are for design guidance only and are not tested or guaranteed. In some graphs or tables the data presented are outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

#### 8. MEMORY

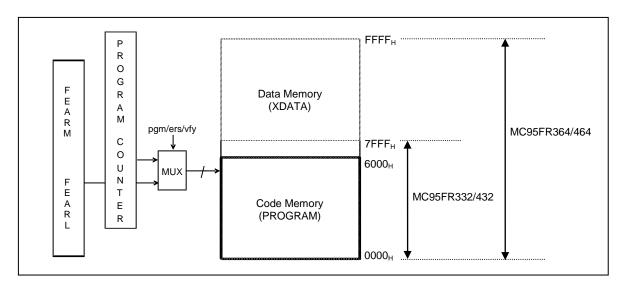

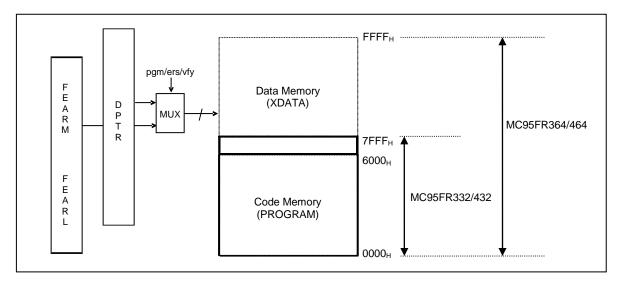

The MC95FR332/432/364/464 has separate address spaces for Program and Data Memory. The logical separation of Program and Data Memory allows the Data Memory to be accessed by 8-bit addresses, which can be more quickly stored and manipulated by an 8-bit CPU. Nevertheless, 16-bit Data Memory addresses can also be generated through the DPTR register.

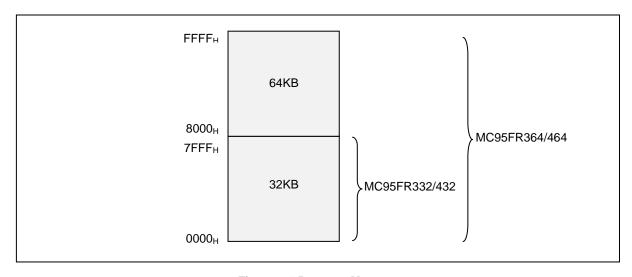

Program Memory contains user software and is read-only while the device is in normal running mode. The MC95FR332/432/364/464 can assign maximum 32KB/64KB to Program Memory.

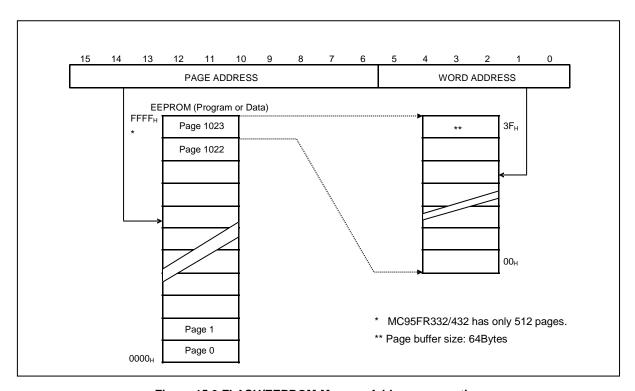

Data Memory is composed of Internal RAM (IRAM), External RAM (XRAM) and Data EEPROM. IRAM is read-writable and address space is 256B including Stack Pointer. XRAM has 1KB of memory depth and also read-writable. The Data EEPROM share the same physical memory with Program Memory and the address space can be varied by configuring registers. As both XRAM and Data EEPROM are accessed via movx instruction, ie, being allotted to XDATA region, the address space assigned to XRAM (0000<sub>H</sub>~03FF<sub>H</sub>,1KB) cannot be used as Data EEPROM. So, the maximum address space for Data EEPROM is 31KB for MC95FR332/432 and 63KB for MC95FR364/464.

NOTE The terms IRAM and XRAM are used just to classify kind of memory. XRAM doesn't have to reside outside the device. In MC95FR332/432/364/464, both IRAM and XRAM reside in device.

#### 8.1 Program Memory

A 16-bit program counter is capable of addressing up to 64K bytes. The following figure shows a map of program memory in MC95FR332/432/364/464. After reset, the CPU begins program execution from address 0000<sub>H</sub>. All interrupt vector is assigned to their fixed location in program memory. An interrupt causes the CPU to jump to it's vector location, where the CPU commences execution of the service routine. External interrupt 0, for example, is assigned to location 000B<sub>H</sub>. If user wants to use external interrupt 0 as an interrupt source, its service routine must begin at location 000B<sub>H</sub>. If the interrupt is not used, its service location is available as general purpose program memory. Because all interrupt vector can use 8 bytes from each vector address NOTE, the service routine can reside entirely within that 8 bytes if an interrupt service routine is short enough (as is often the case in control applications). Noramlly an interrupt service routine is longer than 8 bytes, so the service routine starts with a jump instruction.

NOTE Refer to Table 10-2 Interrupt Vector Address.

Figure 8.1 Program Memory

#### **8.2 IRAM**

Figure 8.2 DATA MEMORY (IRAM)

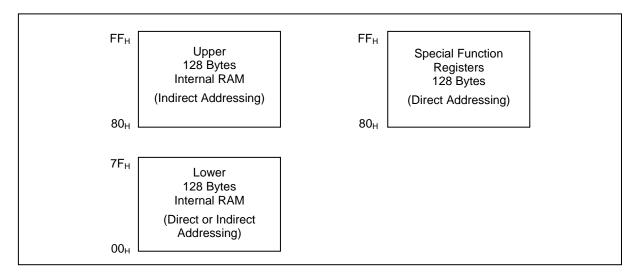

Internal Data Memory is mapped in Figure 8-2. The memory space is shown divided into three blocks, which are generally referred to as the Lower 128, the Upper 128, and SFR space.

Internal Data Memory addresses are always one byte wide, which implies an address space of only 256 bytes. However, the addressing modes for internal RAM can in fact accommodate 384 bytes, using a simple trick. Direct addresss higher than 7F<sub>H</sub> access one memory space, and indirect addresses higher than 7F<sub>H</sub> accessa different memory space. Thus Figure 8-2 showsthe Upper 128 and SFR space occupying the same block of addresses, 80<sub>H</sub> through FF<sub>H</sub>, although they are physically separate entities.

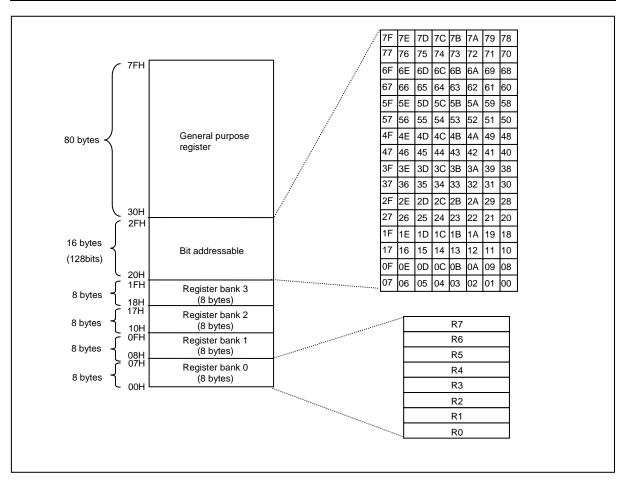

The Lower 128 bytes of RAM are present in all devices using MCS-51 devices as mapped in Figure 8-2. The lowest 32 bytes are grouped into 4 banks of 8 registers. Program instructions call out these registers as R0 through R7. Two bits in the Program Status Word (PSW) select which register bank is in use. This allows more efficient use of code space, since register instructions are shorter than instructions that use direct addressing.

The next 16 bytes above the register banks form a block of bit-addressable memory space. The MCS-51 instruction set includes a wide selection of single-bit instructions, and the 128 bits in this area can be directly addressed by these instructions. The bit addresses in this area are 00<sub>H</sub> through 7F<sub>H</sub>.

All of the bytes in the Lower 128 can be accessed by either direct or indirect addressing. The Upper 128 can only be accessed by indirect addressing. These spaces are used for user RAM and stack pointer.

Figure 8.3 Lower 128 Byte of IRAM

#### 8.2.1 Indirect Address Area

Note that in Figure 8.2 the SFRs and the indirect address RAM have the same addresses ( $80_{H}$ ~FF<sub>H</sub>). Nevertheless, they are two separate areas and accessed in two different ways.

For example the instruction

MOV 80H, #0AAH

writes 0AA<sub>H</sub> to Port 0 which is one of the SFRs and the instruction

MOV R0, #80H

MOV @R0, #0BBH

writes  $0BB_H$  in location  $80_H$  of data RAM. Thus, after execution of both of the above instructions Port 0 will contain  $0AA_H$  and location  $80_H$  of the RAM will contain  $0BB_H$ .

Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data RAM are available as stack space in MC95FR332/432/364/464.

#### 8.2.2 Direct And Indirect Address Area

The 128 bytes of RAM which can be accessed by both direct and indirect addressing can be divided into 3 segments as listed below and shown in Figure 8.3.

**Register Bank 0~3** Locations  $00_H$  through  $1F_H$  (32 bytes). ASM-51 and the device after reset default to register bank 0. To use the other register banks the user must select them in the software (refer to

the MCS-51 Micro Assembler User's Guide). Each register bank contains 8 one-byte registers, 0 through 7.

Reset initializes the Stack Pointer to location  $07_H$  and it is incremented once to start from location  $08_H$  which is the first register (R0) of the second register bank. Thus, in order to use more than one register bank, the SP should be initialized to a different location of the RAM where it is not used for data storage (ie, higher part of the RAM).

**Bit Addressable Area** 16 bytes have been assigned for this segment,  $20_{H}\sim2F_{H}$ . Each one of the 128 bits of this segment can be directly addressed ( $00_{H}\sim7F_{H}$ ).

The bits can be referred to in two ways both of which are acceptable by the ASM-51. One way is to refer to their addresses, ie.  $00_H$  to  $7F_H$ . The other way is with reference to bytes  $20_H$  to  $2F_H$ . Thus, bits  $0_H \sim 7_H$  can also be referred to as bits  $20.0 \sim 20.7$ , and bits  $8_H \sim F_H$  are the same as  $21.0 \sim 21.7$  and so on.

**Scratch Pad Area** Bytes 30<sub>H</sub> through 7F<sub>H</sub> are available to the user as data RAM. However, if the stack pointer has been initialized to this area, enough number of bytes should be left aside to prevent SP data destruction.

#### 8.2.3 Special Function Registers

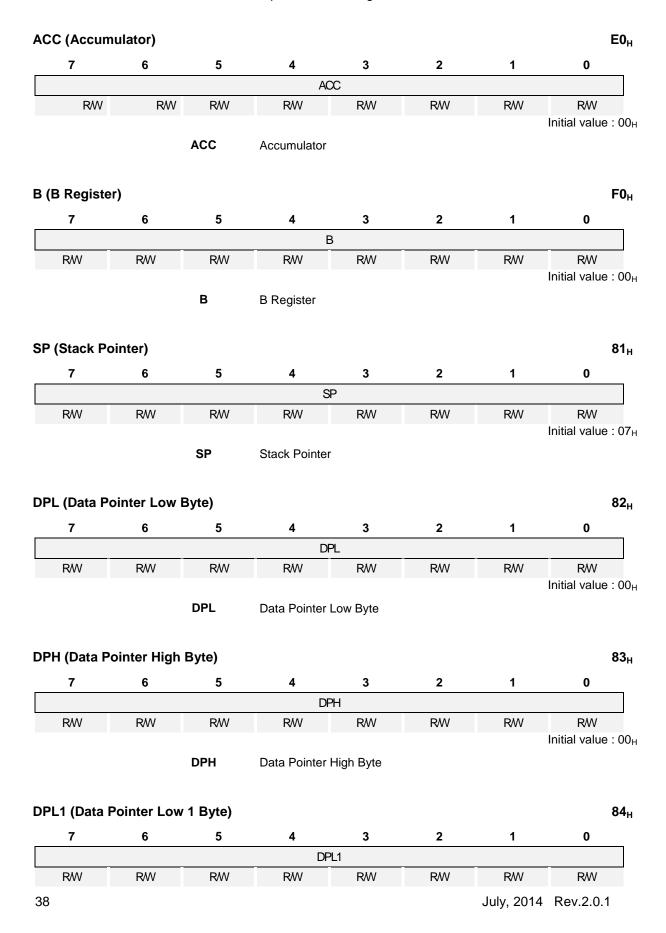

All I/O and peripherals operation for the MC95FR332/432/364/464 accessed via Special Function Registers (SFRs). These registers occupy direct Internal Data Memory space locations in the range  $80_{H}$  to FF<sub>H</sub>. Their names and addresses are given in the Table 8.9. Note these SFRs are implemented using flip-flops within the core, not as RAM.

The MC95FR332/432/364/464 has special registers which are provided by M8051 core. These are Program Counter(PC), Accumulator(A), B register(B), the Stack Pointer(SP), the Program Status Word(PSW), general purpose register(R0~R7) and DPTR (Data pointer register).

NOTE There's some address space in the SFRs which are not implemented. Reading these address space may return arbitrary value, and writing to these reserved SFR address may result in un-expected operation. So cautions are needed when accessing reserved address.

**Accumulator (ACC)** This register provides one of the operands for most ALU operations. It is denoted as 'A' in the instruction table included later in this document. On reset this register returns 00<sub>H</sub>.

**B register (B)** This register provides the second operand for multiply or divide instructions. Otherwise, it may be used as a scratch pad register. On reset this register returns 00<sub>H</sub>.

**Stack Pointer (SP)** The SP register contains the Stack Pointer. The Stack Pointer is used to load the program counter into Internal Data Memory during LCALL and ACALL instructions and to retrieve the program counter from memory during RET and RETI instructions. Data may also be saved on or retrieved from the stack using PUSH and POP instructions. Instructions that manipulate the stack automatically pre-increment or post-decrement the Stack Pointer so that the Stack Pointer always points to the last byte written to the stack, i.e. the top of the stack. On reset the Stack Pointer is set to  $07_{\rm H}$ .

It falls to the programmer to ensure that the location of the stack in Internal Data Memory does not interfere with other data stored therein.

**Program Counter (PC)** The Program Counter consists of two 8-bit registers PCH and PCL. This counter indicates the address of the next instruction to be executed. On reset, the program counter is initialized to reset routine address (PCH:00<sub>H</sub>, PCL:00<sub>H</sub>).

**Data Pointer Register (DPTR)** The Data Pointer (DPTR) is a 16-bit register which is used to form 16-bit addresses for External Data Memory accesses (MOVX A, @DPTR and MOVX @DPTR, A), for program byte moves (MOVC A, @A+DPTR) and for indirect program jumps (JMP @A+DPTR).

Two true 16-bit operations are allowed on the Data Pointer – load immediate (MOV DPTR, #data) and increment (INC DPTR).

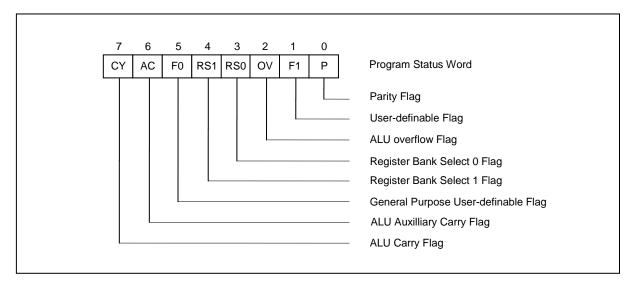

**Program Status Word (PSW)** The PSW contains several status bits that reflect the current state of the CPU. The PSW, shown in Figure 8.1, resides in SFR space. It contatins the Carry bit, the Auxiliary Carry (for BCD operations), the two register bank select bits, the Overflow flag, a Parity bit, and two user-definable status flags.

**CY** The Carry bit, other than serving the function of a Carry bit in arithmetic operations, also serves as the "Accumulator" for a number of Boolean operations.

**AC** The Auxiliary Carry bit, this bit is set when there is a carry from bit 3 of ALU or there is no borrow from bit 4 of ALU after operation.

**RS0**, **RS1** The bits RS0 and RS1 are used to select one of the four register banks shown in Figure 8.3. A number of instructions refer to these RAM locations as R0 through R7. The selection of which of the four banks is being referred to is made on the basis of the bits RS0 and RS1 at execution time.

**OV** Overflow flag. This bit is set to "1" when an overflow occurs as the result of an arithmetic operation involving signs. An overflow occurs when the result of an addition or subtraction exceeds  $+127(7F_H)$  or  $128(80_H)$ . The CLRV instruction clears the overflow flag. There is no set instruction. When the BIT instruction is executed, bit 6 of memory is copied to this flag.

**P** The Parity bit reflects the number of 1s in the Accumulator: P=1 if the Accumulator contains an odd number of 1s, and P=0 if the Accumulator contains an even number of 1s. Thus the number of 1s in the Accumulator plus P is always even.

Two bits in the PSW are uncommitted and may be used as general purpose status flags.

Figure 8.4 PSW Register

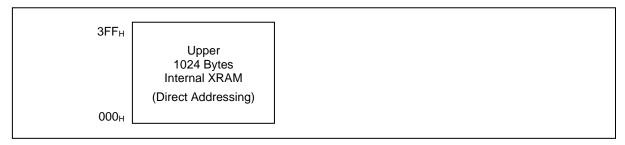

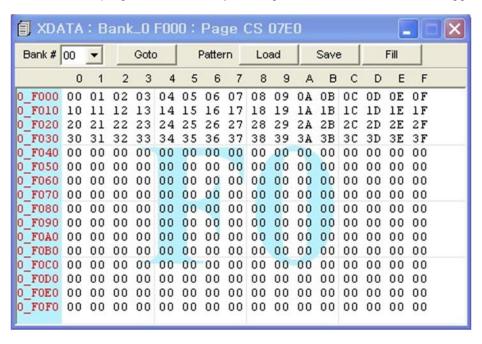

#### **8.3 XRAM**

There's another kind of RAM called XRAM (External RAM) in MC95FR332/432/364/464 and the size is 1KB, 0000<sub>H</sub> through 03FF<sub>H</sub>. This address space is assigned to XDATA region and used for data

storage. In MC95FR332/432/364/464, two kinds of Data Memory are assigned to XDATA region which are XRAM and Data EEPROM. So the address of two data memories do not duplicate. In other words, addresses higher than 03FF<sub>H</sub> accesses Data EEPROM if the address space is assigned as Data EEPROM.

Figure 8.5 DATA MEMORY (XRAM)

#### 8.4 Data EEPROM

As described previously, MC95FR332/432/364/464 has 32KB/64KB of Program Memory called FLASH. User software can divide this FLASH memory into two memory space, Program Memory and Data EEPROM. If devided, lower address space from 0000<sub>H</sub> is used for Program Memory and higher address space upto 7FFF<sub>H</sub>/FFFF<sub>H</sub> are used for Data EEPROM. Like External RAM, Data EEPROM is also assigned to XDATA region, therefore the bottom address of Data EEPROM must higher than 03FF<sub>H</sub>. Logically the maximum size of Data EEPROM is 31KB/63KB, addresses from 0400<sub>H</sub> through 7FFF<sub>H</sub>/FFFF<sub>H</sub>. After reset, the entire FLASH memory is assigned to Program Memory.

# 8.5 SFR map

# 8.5.1 SFR Map Summary

- Reserved

M8051 Compatible

|                 | 0H/8H <sup>NOTE</sup> | 1H/9H             | 2H/AH              | 3H/BH                 | 4H/CH                 | 5H/DH             | 6H/EH              | 7H/FH               |

|-----------------|-----------------------|-------------------|--------------------|-----------------------|-----------------------|-------------------|--------------------|---------------------|

| F8 <sub>H</sub> | IP1<br>00_0000        | -                 | FUSE_CAL<br>2      | -                     | -                     | FUSE_CON<br>F     | TEST_B             | TEST_A              |

| F0 <sub>H</sub> | B<br>0000_0000        | -                 | FEARL              | FEARM                 | FEARH                 | FEDR              | -                  | -                   |

| E8 <sub>H</sub> | RMR                   | -                 | FEMR               | FECR                  | FESR                  | FETCR             | DEARL              | DEARM               |

| E0 <sub>H</sub> | ACC<br>0000_0000      | -                 | UCTRL1             | UCTRL2                | UCTRL3                | USTAT             | UBAUD              | UDATA               |

| D8 <sub>H</sub> | P2BPC<br>111          | DISTR             | P5<br>0000         | P5IO<br>0000          | P5PU<br>1111          | P5OD<br>0000      | P5BPC<br>1111      | VWCDR               |

| D0 <sub>H</sub> | PSW<br>0000_0000      | -                 | SMRR0              | SMRR1                 | -                     | -                 | SRLC0              | SRLC1               |

| С8н             | P1BPC<br>1111_1111    | T3CR2             | T3CR               | T3L/CDR3L/<br>PWM3DRL | T3H/CDR3H<br>/PWM3DRH | T3DRL/PW<br>M3PRL | T3DRH/PW<br>M3PRH  | T2L/T2DRL/<br>CDR2L |

| C0 <sub>H</sub> | P0BPC<br>1111_1111    | P0PC<br>0000_0000 | RDRH               | RDRL                  | -                     | -                 | T2CR               | T2H/T2DRH<br>/CDR2H |

| B8 <sub>H</sub> | IP<br>00_0000         | P2OD<br>000       | -                  | CFRH                  | CFRL                  | CRC               | RODR               | ROB                 |

| B0 <sub>H</sub> | P2IO<br>000           | P1OD<br>0000_0000 | T0CR               | T0/CDR0/T0<br>DR      | T1CR                  | T1DR/<br>PWM1PR   | T1/CDR1/<br>PWM1DR | PWM1HR              |

| A8 <sub>H</sub> | IE<br>0000_0000       | IE1               | IE2                | IE3                   | EIFLAG                | EIEDGE            | EIPOLA             | EIENAB              |

| A0 <sub>H</sub> | P1IO<br>0000_0000     | -                 | EO<br>0000_0000    | P4<br>0000_0000       | P4IO<br>0000_0000     | P4PU<br>1111_1111 | P4OD<br>0000_0000  | P4BPC<br>1111_1111  |

| 98 <sub>H</sub> | P0IO<br>0000_0000     | P2PU<br>000       | P3BPC<br>1111_1111 | P3IO<br>0000_0000     | P3PU<br>0011_1100     | P3OD<br>0000_0000 | -                  | P3<br>0000_0000     |

| 90 <sub>H</sub> | P2<br>000             | P1PU<br>0000_0000 | -                  | -                     | -                     | -                 | -                  | -                   |

| 88 <sub>H</sub> | P1<br>0000_0000       | P0PU<br>0000_0000 | SCCR               | BCCR                  | BITR                  | WDTMR             | WDTR               | BODSR               |

| 80 <sub>H</sub> | P0<br>0000_0000       | SP<br>0000_0111   | DPL<br>0000_0000   | DPH<br>0000_0000      | DPL1<br>0000_0000     | DPH1<br>0000_0000 | BODR<br>1000_0001  | PCON<br>0000_0000   |

Table 8-1 SFR Map

**Caution**: Writing to reserved registers may result in un-expected function.

$<sup>^{\</sup>mbox{\scriptsize NOTE}}$  These registers are bit-addressable.

### 8.5.2 Compiler Compatible SFR

Refer to section 8.2.3 for detailed description of these registers.

Initial value : 00<sub>H</sub>

**DPL1** Data Pointer Low 1 Byte

### **DPH1 (Data Pointer High 1 Byte)** 85<sub>H</sub> 5 2 7 6 4 3 1 0 DPH1 RW RW RW RW RW RW RW RW Initial value: 00H DPH1 Data Pointer High 1 Byte **PSW (Program Status Word)** $D0_{H}$ 7 5 2 6 3 1 0 4 CY AC F0 RS1 RS0 OV F1 Ρ RW RW RW RW RW RW RW RW Initial value: 00H CY Carry Flag. Receives carry out from bit 1 fo ALU operands. AC Auxiliary Carry Flag. Receives carry out from bit 1 of addition operands. F0 General Purpose Status Flag RS<sub>1</sub> Register Bank Selection bit 1 RS0 Register Bank Selection bit 0 ٥٧ Overflow Flag. Set by arithmetic operations. F1 User-definable Flag P Parity of ACC. Set by hardware to 1 if it contains contains an odd number of 1s, otherwise it is reset to 0. **EO (Extended Operation Register)** $A2_H$ 7 6 5 4 3 2 1 0 \_ TRAP\_EN DPSEL2 DPSEL1 DPSEL.0 R R R RW R RW RW RW

**TRAP\_EN** Select the instruction between software TRAP and MOVC @(DPTR++), A.

0 Select software TRAP instruction.

Select MOVC @(DPTR++), A instruction.

# DPSEL[2:0] Select DPT R.

| 00.000 2. |                       |                                 |                                       |

|-----------|-----------------------|---------------------------------|---------------------------------------|

| DPSEL2    | DPSEL1                | DPSEL0                          |                                       |

| 0         | 0                     | 0                               | DPTP0.                                |

| 0         | 0                     | 1                               | DPTP1.                                |

| 0         | 1                     | 0                               | Reserved                              |

| 0         | 1                     | 1                               | Reserved                              |

| 1         | 0                     | 0                               | Reserved                              |

| 1         | 0                     | 1                               | Reserved                              |

| 1         | 1                     | 0                               | Reserved                              |

| 1         | 1                     | 1                               | Reserved                              |

|           | 0<br>0<br>0<br>0<br>1 | 0 0 0 0 0 0 0 1 0 1 1 0 1 1 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

Initial value: 00H

### **9. I/O PORTS**

### 9.1 Introduction

The MC95FR332/432/364/464 has six I/O ports (P0, P1, P2, P3, P4, P5). Each port can be easily configured by software whether to use internal pull up resistor or not, whether to use open drain output or not, or whether the pin is input or output. Also P0 includes function that can generate interrupt when the state of P0 changes.

### 9.2 Register Description

### 9.2.1 Data Register (Px)

Data Register is a bidirectional I/O port. If ports are configured as output ports, data can be written to the corresponding bit in the Px. If ports are configured as input ports, the port value can be read from the corresponding bit in the Px.

### 9.2.2 Direction Register (PxIO)

The PxnIO bit in the PxIO register selects the direction of this pin. If PxnIO is written logic one, Pxn is configured as an output pin. If PxnIO is written logic zero, Pxn is configured as an input pin. All bits are cleared by a system reset.

### 9.2.3 Pull-up Resistor Selection Register (PxPU)

All ports P0, P1, P2, P3, P4, P5 have optional internal pull-ups. The PxnPU bit in the PxPU register allows the use of pull-up resistor. If PxnPU is written logic one, the pull-up resistor is activated. If PxnPU is written logic zero, the pull-up resistor is deactivated. When the port is configured as an input port, internal pull-up is deactivated regardless of the PxnPU bit. After reset, all pull-up resistors are switched off except those of P3[5:2], P4[7:0], P5[3:0]. According to PKG types, some of these ports are omiited, so to maintain input status, the internal pull-ups for these ports are activated.

### 9.2.4 Open-drain Selection Register (PxOD)

The PxnOD bit in the PxOD register controls the port type when configured as an output port. If PxnOD is written logic one, the port becomes open-drain type. If PxnOD is written logic zero, the port becomes push-pull type. After reset, open-drain function is disabled.

**Caution**: Port 0 has no open drain control register.

### 9.2.5 Pull-up Control Register (PxBPC)

When the external VDD drops below the BODOUT0 level, the ports can be selectively configured as input ports with pull-up resistors activated regardless of the PxnIO. In this case, the port direction is changed by hardware automatically. If PxnBPC is written logic one, this function is enabled. If PxnBPC is written logic zero, the port maintain its status even if the device enters stop mode after the external VDD is fallen below the BODOUT0 level. After reset, PxnBPC is set to 1 allowing automatic port direction change due to voltage drop.

## 9.2.6 Pin Change Interrupt Enable Register (P0PC)

P0 port support Pin Change Interrupt (PCI) function. Pin Change Interrupt will trigger if any pin changes its status when P0nPC is set to 1. At reset, PCI function is disabled for all P0 pins.

# 9.2.7 Register Map

| Name  | Address         | Dir | Default         | Description                             |  |  |

|-------|-----------------|-----|-----------------|-----------------------------------------|--|--|

| P0    | 80н             | R/W | 00 <sub>H</sub> | P0 Data Register                        |  |  |

| P0IO  | 98 <sub>H</sub> | R/W | 00 <sub>H</sub> | P0 Direction Register                   |  |  |

| P0PU  | 89 <sub>H</sub> | R/W | 00 <sub>H</sub> | P0 Pull-up Resistor Selection Register  |  |  |

| P0BPC | СОн             | R/W | FF <sub>H</sub> | P0 Pull-up Control Register             |  |  |

| P0PC  | C1 <sub>H</sub> | R/W | 00 <sub>H</sub> | P0 Pin Change Interrupt Enable Register |  |  |

| P1    | 88 <sub>H</sub> | R/W | 00 <sub>H</sub> | P1 Data Register                        |  |  |

| P1IO  | A0 <sub>H</sub> | R/W | 00 <sub>H</sub> | P1 Direction Register                   |  |  |

| P1PU  | 91 <sub>H</sub> | R/W | 00 <sub>H</sub> | P1 Pull-up Resistor Selection Register  |  |  |

| P1OD  | B1 <sub>H</sub> | R/W | 00 <sub>H</sub> | P1 Open-drain Selection Register        |  |  |

| P1BPC | C8 <sub>H</sub> | R/W | FF <sub>H</sub> | P1 Pull-up Control Register             |  |  |

| P2    | 90 <sub>H</sub> | R/W | 00 <sub>H</sub> | P2 Data Register                        |  |  |

| P2IO  | ВОн             | R/W | 00 <sub>H</sub> | P2 Direction Register                   |  |  |

| P2PU  | 99              | R/W | 00 <sub>H</sub> | P2 Pull-up Resistor Selection Register  |  |  |

| P2OD  | В9н             | R/W | 00 <sub>H</sub> | P2 Open-drain Selection Register        |  |  |

| P2BPC | D8 <sub>H</sub> | R/W | 07 <sub>H</sub> | P2 Pull-up Control Register             |  |  |

| P3    | 9F <sub>H</sub> | R/W | 00 <sub>H</sub> | P3 Data Register                        |  |  |

| P3IO  | 9Вн             | R/W | 00 <sub>H</sub> | P3 Direction Register                   |  |  |

| P3PU  | 9Сн             | R/W | 3Сн             | P3 Pull-up Resistor Selection Register  |  |  |

| P3OD  | 9D <sub>H</sub> | R/W | 00 <sub>H</sub> | P3 Open-drain Selection Register        |  |  |

| P3BPC | 9Ан             | R/W | FF <sub>H</sub> | P3 Pull-up Control Register             |  |  |

| P4    | A3 <sub>H</sub> | R/W | 00 <sub>H</sub> | P4 Data Register                        |  |  |

| P4IO  | A4 <sub>H</sub> | R/W | 00 <sub>H</sub> | P4 Direction Register                   |  |  |

| P4PU  | A5 <sub>H</sub> | R/W | FF <sub>H</sub> | P4 Pull-up Resistor Selection Register  |  |  |

| P4OD  | A6 <sub>H</sub> | R/W | 00 <sub>H</sub> | P4 Open-drain Selection Register        |  |  |

| P4BPC | A7 <sub>H</sub> | R/W | FF <sub>H</sub> | P4 Pull-up Control Register             |  |  |

| P5    | DA <sub>H</sub> | R/W | 00 <sub>H</sub> | P5 Data Register                        |  |  |

| P5IO  | DB <sub>H</sub> | R/W | 00 <sub>H</sub> | P5 Direction Register                   |  |  |

| P5PU  | DC <sub>H</sub> | R/W | 0F <sub>H</sub> | P5 Pull-up Resistor Selection Register  |  |  |

| P5OD  | DD <sub>H</sub> | R/W | 00 <sub>H</sub> | P5 Open-drain Selection Register        |  |  |

| P5BPC | DE <sub>H</sub> | R/W | 0F <sub>H</sub> | P5 Pull-up Control Register             |  |  |

**Table 0-1 Register Map of Port**

## 9.2.8 PORT 0

| ı | P0 (P0 Data Register) 80 <sub>H</sub> |     |     |     |     |     |     |     |  |  |  |

|---|---------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

|   | 7                                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|   | P07                                   | P06 | P05 | P04 | P03 | P02 | P01 | P00 |  |  |  |

|   | RW                                    | RW  | RW  | RW  | RW  | RW  | RW  | RW  |  |  |  |

Initial value: 00<sub>H</sub>

### P0[7:0] I/O Data P0IO (P0 Direction Register) 98<sub>H</sub> 6 5 2 4 3 1 0 P07IO P06IO P04IO P03IO P02IO P01IO P05IO P001O RW RW RW RW RW RW RW RW Initial value: 00<sub>H</sub> P0IO[7:0] P0 Direction 0 Input 1 Output P0PU (P0 Pull-up Resistor Selection Register) 89<sub>H</sub> 7 6 5 4 3 2 1 0 P07PU P06PU P05PU P04PU P03PU P02PU P01PU P00PU RW RW RW RW RW RW RW RW Initial value: 00<sub>H</sub> P0PU[7:0] P0 Pull-up Control 0 Disable pull-up Enable pull-up 1 P0BPC (P0 Pull-up Control Register) C<sub>0</sub>H 7 6 5 2 1 0 4 3 P07BPC P06BPC P05BPC P04BPC P03BPC P02BPC P01BPC P00BPC RW RW RW RW RW RW RW RW Initial value: FFH P0BPC[7:0] Controls port direction and use of internal pull-up resistor when external VDD drops below BODOUT0 level. Maintain its previous state (input or output) 1 Changed to input port and pull-up resistor is activated POPC (P0 Pin Change Interrupt Enable Register) C1<sub>H</sub> 7 6 5 3 2 1 0 P04PC P01PC P07PC P06PC P05PC P03PC P02PC P00PC RW RW RW RW RW RW RW RW Initial value: 00H P0PC[7:0] Controls Pin Change Interrupt function 0 Disable PCI function 1 **Enable PCI function** 9.2.9 PORT 1 н

| P1 (P1 Data | Register) |   |   |   |   |   | 88 <sub>H</sub> |

|-------------|-----------|---|---|---|---|---|-----------------|

| 7           | 6         | 5 | 4 | 3 | 2 | 1 | 0               |

|             |           |   |   |   |   |   |                 |

| P17 | P16 | P15 | P14 | P13 | P12 | P11 | P10 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| RW  |

Initial value: 00<sub>H</sub>

P1[7:0] I/O Data

## P1IO (P1 Direction Register)

$A0_{H}$

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P17IO | P16IO | P15IO | P14IO | P13IO | P12IO | P11IO | P10IO |

| RW    |

Initial value: 00<sub>H</sub>

P1IO[7:0] P1 Direction

0 Input

1 Output

### P1PU (P1 Pull-up Resistor Selection Register)

91<sub>H</sub>

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P17PU | P16PU | P15PU | P14PU | P13PU | P12PU | P11PU | P10PU |

| RW    |

Initial value: 00H

P1PU[7:0] P1 Pull-up Control

0 Disable pull-up

1 Enable pull-up

## P10D (P1 Open-drain Selection Register)

B<sub>1</sub><sub>H</sub>

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P170D | P160D | P15OD | P140D | P130D | P120D | P11OD | P100D |

| RW    |

Initial value: 00<sub>H</sub>

**P10D[7:0]** Controls P1 port type when configured as output port.

0 Push-pull type output drive

1 Open-drain type output drive

### P1BPC (P1 Pull-up Control Register)

C8<sub>H</sub>

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| P17BPC | P16BPC | P15BPC | P14BPC | P13BPC | P12BPC | P11BPC | P10BPC |

| RW     |

Initial value: FF<sub>H</sub>

P1BPC[7:0]

Controls port direction and use of internal pull-up resistor when external VDD drops below BODOUT0 level.

0 Maintain its previous state (input or output)

1 Changed to input port and pull-up resistor is activated

### 9.2.10 PORT 2

### P2 (P2 Data Register)

90<sub>H</sub>

| 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |

|---|---|---|---|---|-----|-----|-----|

| - | - | - | - | 1 | P22 | P21 | P20 |

| - | - | - | - | - | RW  | RW  | RW  |

Initial value: 00<sub>H</sub>

**P2[2:0]** I/O Data

### P2IO (P2 Direction Register)

B<sub>0</sub><sub>H</sub>

| 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|---|---|---|---|---|-------|-------|-------|

| - | - | - | - | - | P2210 | P211O | P201O |

| - | - | - | - | - | RW    | RW    | RW    |

Initial value: 00<sub>H</sub>

**P2IO[2:0]** P2 Direction NOTE

0 Input

1 Output

### P2PU (P2 Pull-up Resistor Selection Register)

99<sub>H</sub>

| 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|---|---|---|---|---|-------|-------|-------|

| - | - | - | - | - | P22PU | P21PU | P20PU |

| - | - | - | - | - | RW    | RW    | RW    |

Initial value: 00H

P2PU[2:0] P2 Pull-up Control NOTE

0 Disable pull-up

1 Enable pull-up

### P2OD (P2 Open-drain Selection Register)

**B9**<sub>H</sub>

| 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|---|---|---|---|---|-------|-------|-------|

| - | - | - | - | - | P220D | P210D | P200D |

| - | - | - | - | - | RW    | RW    | RW    |

Initial value: 00<sub>H</sub>

**P2OD[2:0]** Controls P2 port type when configured as output port.

0 Push-pull type output drive

1 Open-drain type output drive

### P2BPC (P2 Pull-up Control Register)

D8<sub>H</sub>

| 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0      |

|---|---|---|---|---|--------|--------|--------|

| - | - | - | - | - | P22BPC | P21BPC | P20BPC |

| - | - | - | - | - | RW     | RW     | RW     |

Initial value: 07<sub>H</sub>

NOTE P20 is used as an external reset source when RSTDIS bit in FUSE\_CONF register is cleared. In this case, the direction of P20 is input only and the internal pull-up resistor is always activated regardless of the P20IO or P20PU bits.

### P2BPC[2:0]

Controls port direction and use of internal pull-up resistor when external VDD drops below BODOUT0 level.

- 0 Maintain its previous state (input or output)

- 1 Changed to input port and pull-up resistor is activated

### 9.2.11 PORT 3

### P3 (P3 Data Register)

9F<sub>H</sub>

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P37 | P36 | P35 | P34 | P33 | P32 | P31 | P30 |

| RW  |

Initial value: 00<sub>H</sub>

**P3[7:0]** I/O Data

## P3IO (P3 Direction Register)

9B<sub>H</sub>

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P371O | P36IO | P3510 | P34IO | P33IO | P321O | P31IO | P30IO |

| RW    |

Initial value: 00<sub>H</sub>

P3IO[7:0] P3 Direction

0 Input

1 Output

### P3PU (P3 Pull-up Resistor Selection Register)

9C<sub>H</sub>

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P37PU | P36PU | P35PU | P34PU | P33PU | P32PU | P31PU | P30PU |

| RW    |

Initial value: 3CH

P3PU[7:0] P3 Pull-up Control

0 Disable pull-up

1 Enable pull-up

### P3OD (P3 Open-drain Selection Register)

9D<sub>H</sub>

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P370D | P360D | P35OD | P340D | P33OD | P320D | P310D | P300D |

| RW    |

Initial value: 00H

**P30D[7:0]** Controls P0 port type when configured as output port.

0 Push-pull type output drive

1 Open-drain type output drive

# P3BPC (P3 Pull-up Control Register)

$9A_H$

7 6 5 4 3 2 1 0

| P37BPC | P36BPC | P35BPC | P34BPC | P33BPC | P32BPC | P31BPC | P30BPC |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RW     |

Initial value: FF<sub>H</sub>

### P3BPC[7:0]

Controls port direction and use of internal pull-up resistor when external VDD drops below BODOUT0 level.

- 0 Maintain its previous state (input or output)

- 1 Changed to input port and pull-up resistor is activated

### 9.2.12 PORT 4

## P4 (P4 Data Register)

A3<sub>H</sub>

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P47 | P46 | P45 | P44 | P43 | P42 | P41 | P40 |

| RW  |

Initial value: 00H

P4[7:0] I/O Data

### P4IO (P4 Direction Register)

$A4_H$

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P47IO | P46IO | P45IO | P4410 | P43IO | P42IO | P41IO | P40IO |

| RW    |

Initial value: 00<sub>H</sub>

P4IO[7:0] P4 Direction

0 Input

1 Output

# P4PU (P4 Pull-up Resistor Selection Register)

$A4_{H}$

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P47PU | P46PU | P45PU | P44PU | P43PU | P42PU | P41PU | P40PU |

| RW    |

Initial value : FF<sub>H</sub>

P4PU[7:0] P4 Pull-up Control

0 Disable pull-up

1 Enable pull-up

## P4OD (P4 Open-drain Selection Register)

A<sub>6</sub>H

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P47OD | P46OD | P45OD | P440D | P43OD | P42OD | P410D | P400D |

| RW    |

Initial value: 00H

**P4OD[7:0]** Controls P0 port type when configured as output port.

0 Push-pull type output drive

1 Open-drain type output drive

### P4BPC (P4 Pull-up Control Register)

$A7_{H}$

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| P47BPC | P46BPC | P45BPC | P44BPC | P43BPC | P42BPC | P41BPC | P40BPC |

| RW     |

Initial value: FFH

### P4BPC[7:0]

Controls port direction and use of internal pull-up resistor when external VDD drops below BODOUT0 level.

- 0 Maintain its previous state (input or output)

- 1 Changed to input port and pull-up resistor is activated

### 9.2.13 PORT 5

## P5 (P5 Data Register)

$DA_H$

| 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|---|---|---|---|-----|-----|-----|-----|

| - | - | - | - | P53 | P52 | P51 | P50 |

| - | - | - | - | RW  | RW  | RW  | RW  |

Initial value: 00<sub>H</sub>

P5[3:0] I/O Data

## P5IO (P5 Direction Register)

$\mathsf{DB}_\mathsf{H}$

| 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

|---|---|---|---|-------|-------|-------|-------|

| - | - | - | - | P53IO | P52IO | P51IO | P50IO |

| - | - | - | - | RW    | RW    | RW    | RW    |

Initial value: 00<sub>H</sub>

P5IO[3:0] P5 Direction

0 Input

1 Output

### P5PU (P5 Pull-up Resistor Selection Register)

DCH

| 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

|---|---|---|---|-------|-------|-------|-------|

| - | - | - | - | P53PU | P52PU | P51PU | P50PU |

| - | - | - | - | RW    | RW    | RW    | RW    |

Initial value: 0F<sub>H</sub>

P5PU[3:0] P5 Pull-up Control

0 Disable pull-up

1 Enable pull-up

### P50D (P5 Open-drain Selection Register)

$\text{DD}_{\text{H}}$

| 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

|---|---|---|---|-------|-------|-------|-------|

| - | - | - | - | P53OD | P52OD | P51OD | P50OD |

| - | - | - | - | RW    | RW    | RW    | RW    |

Initial value: 00<sub>H</sub>

## P5OD[3:0]

Controls P0 port type when configured as output port.

- 0 Push-pull type output drive

- 1 Open-drain type output drive

### P5BPC (P5 Pull-up Control Register)

$DE_H$

| 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|---|---|---|---|--------|--------|--------|--------|

| - | - | - | - | P53BPC | P52BPC | P51BPC | P50BPC |

| - | - | - | - | RW     | RW     | RW     | RW     |

Initial value: 0FH

### P5BPC[3:0]

Controls port direction and use of internal pull-up resistor when external VDD drops below BODOUT0 level.

- 0 Maintain its previous state (input or output)

- 1 Changed to input port and pull-up resistor is activated

### 10. INTERRUPT CONTROLLER

## 10.1 Overview

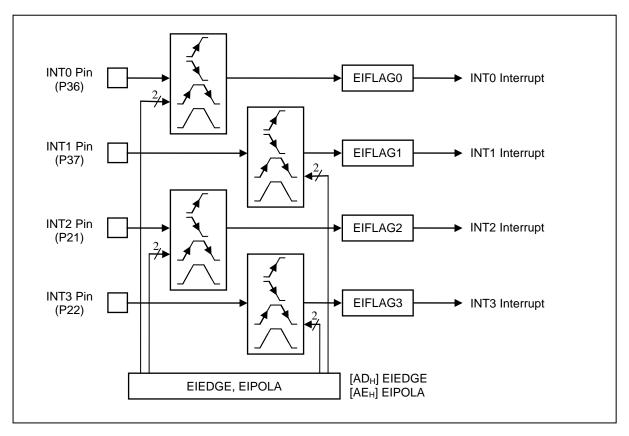

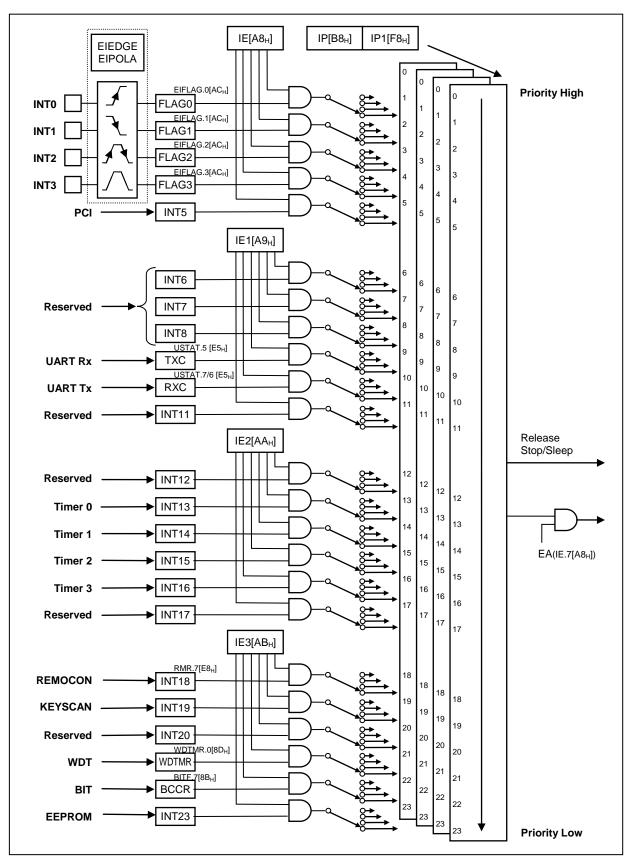

The interrupt controller has the following features to handle interrupt request from internal peripherals or external pins.

- support up to 16 interrupt sources NOTE

- 6 group of 4 priority level

- multiple interrupts handling

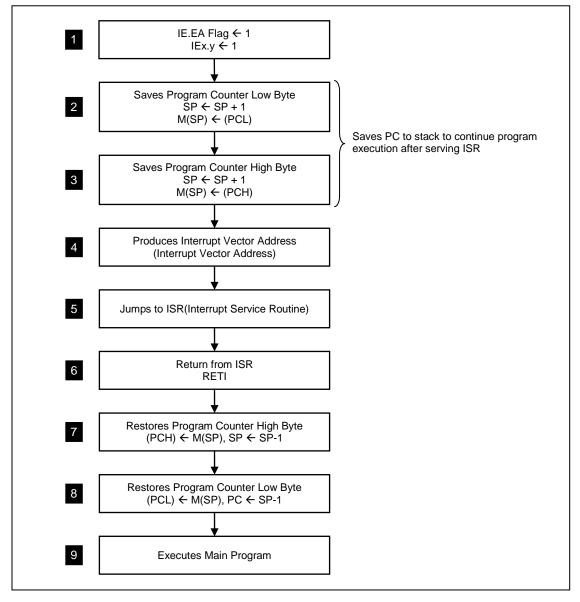

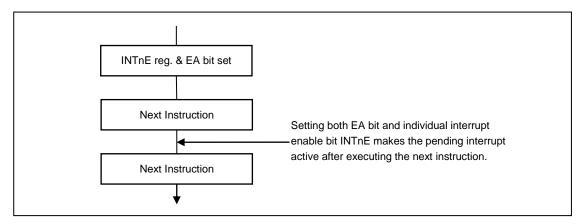

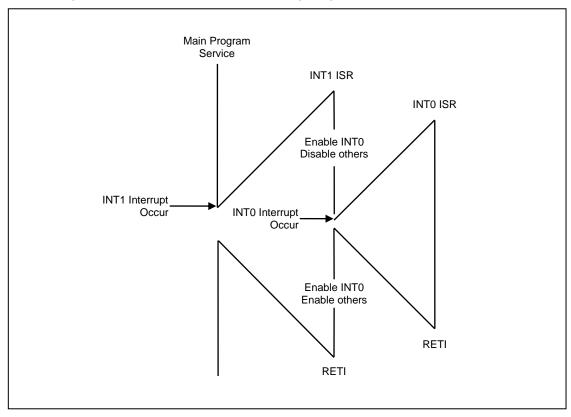

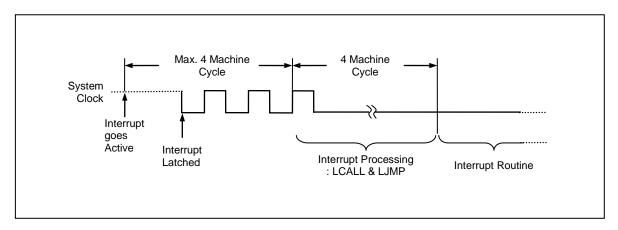

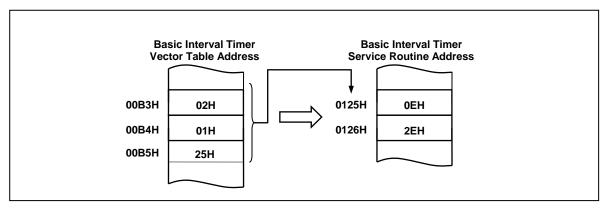

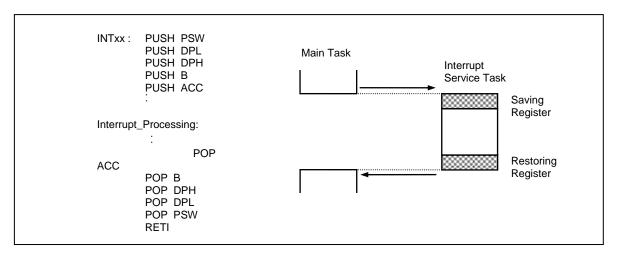

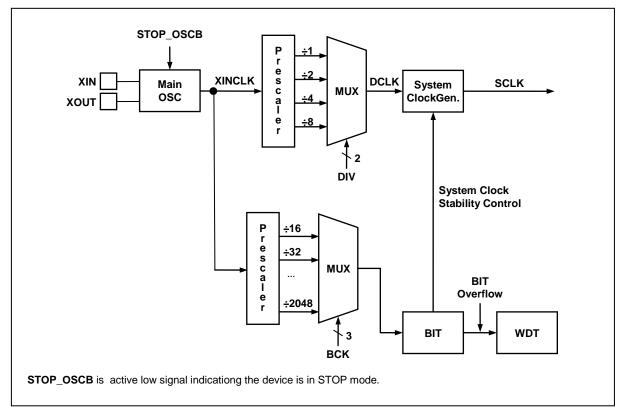

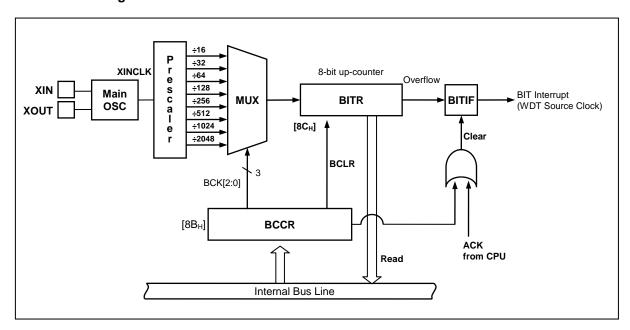

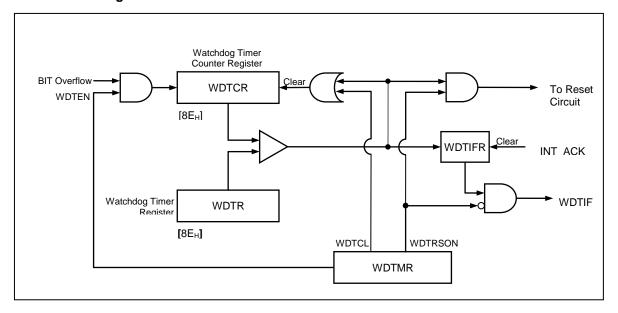

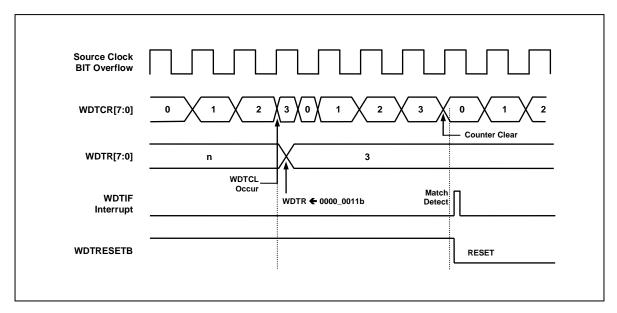

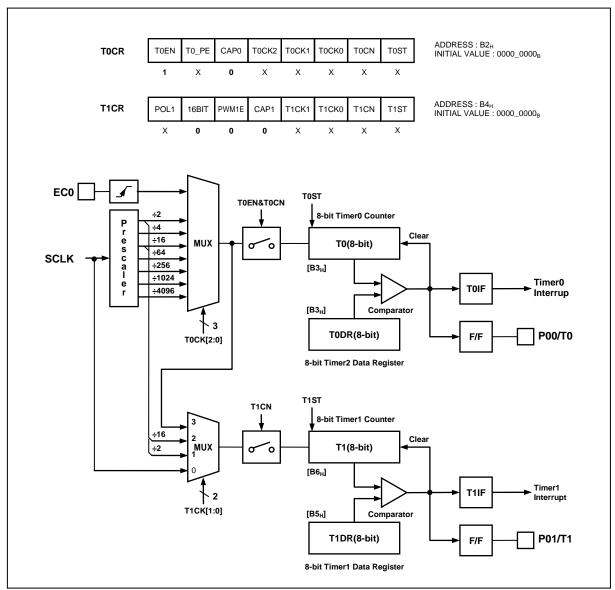

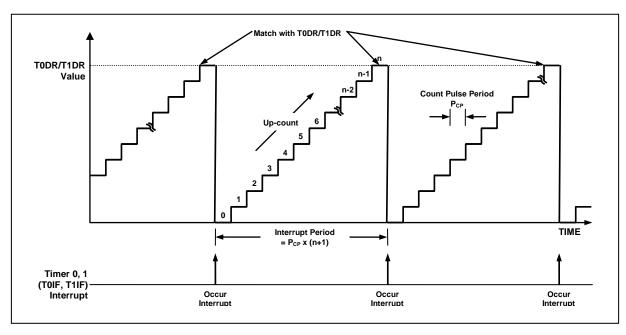

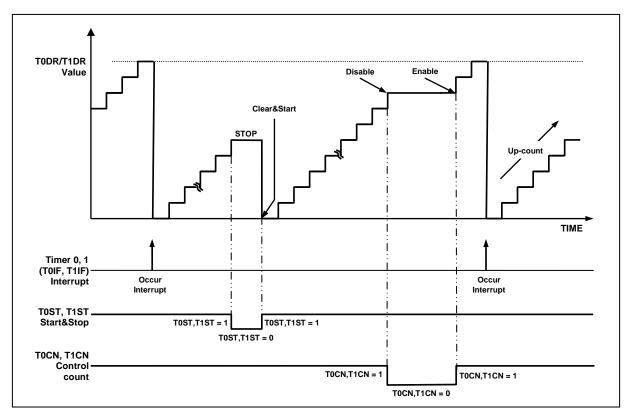

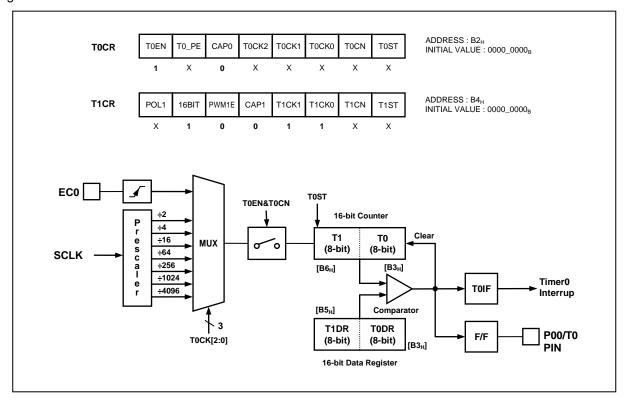

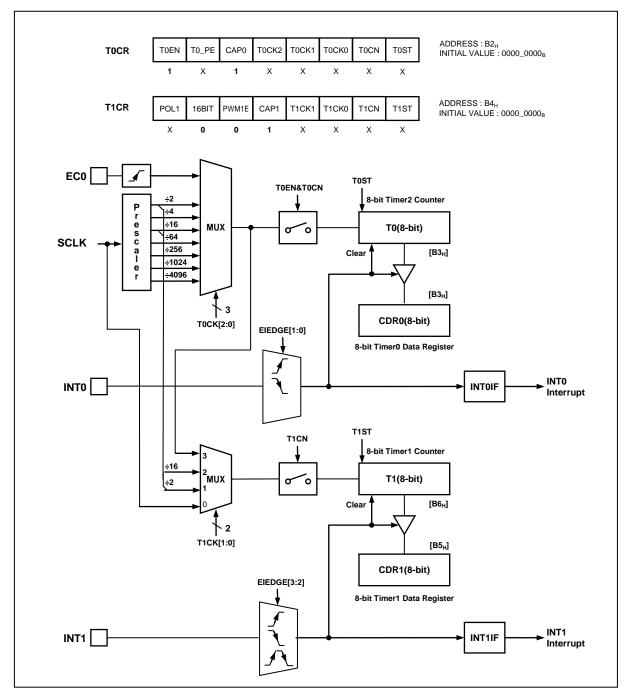

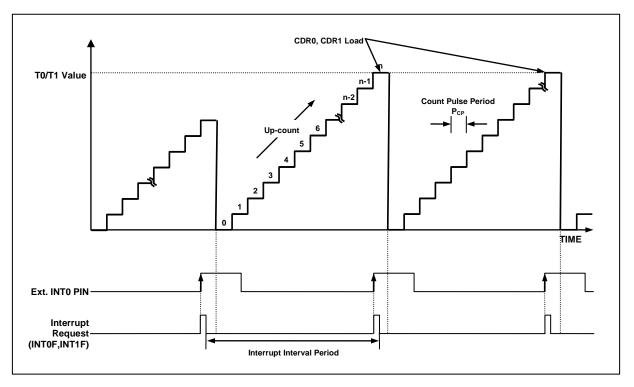

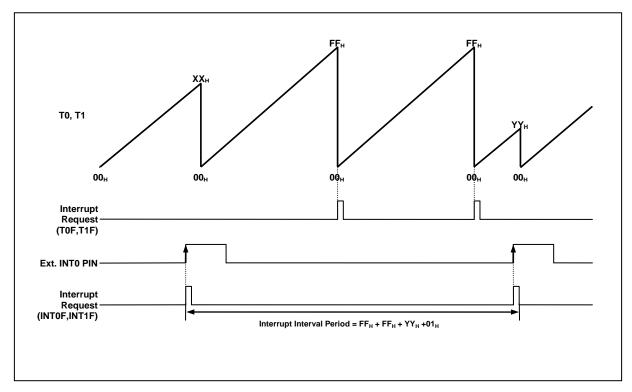

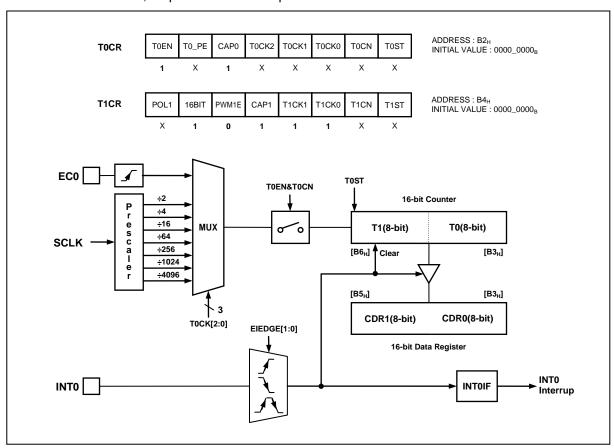

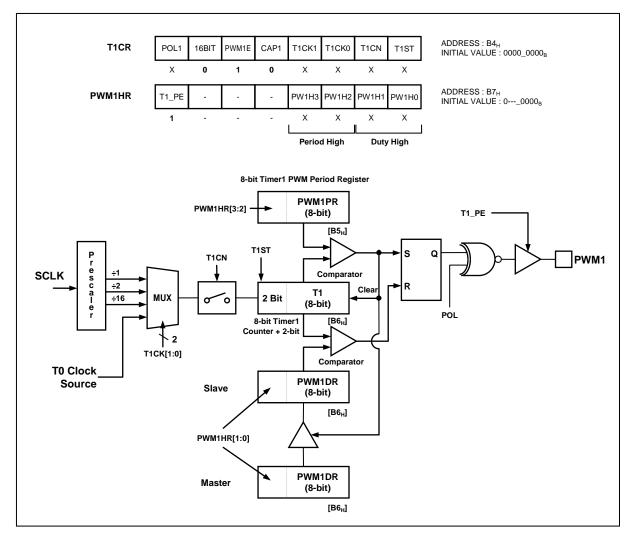

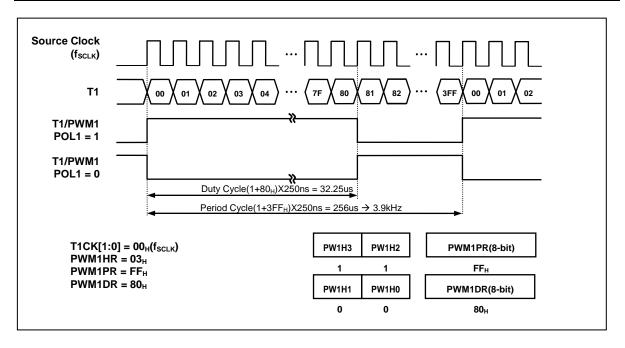

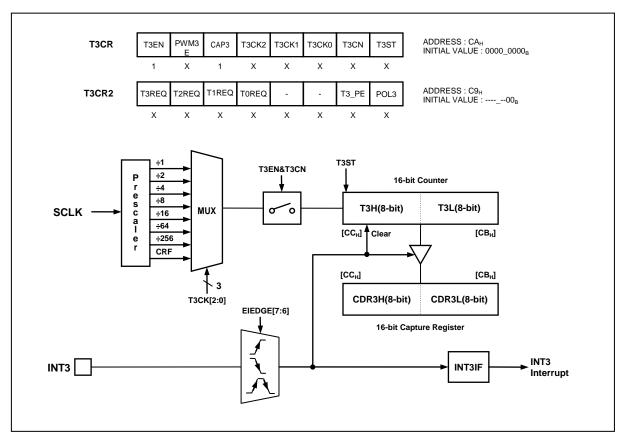

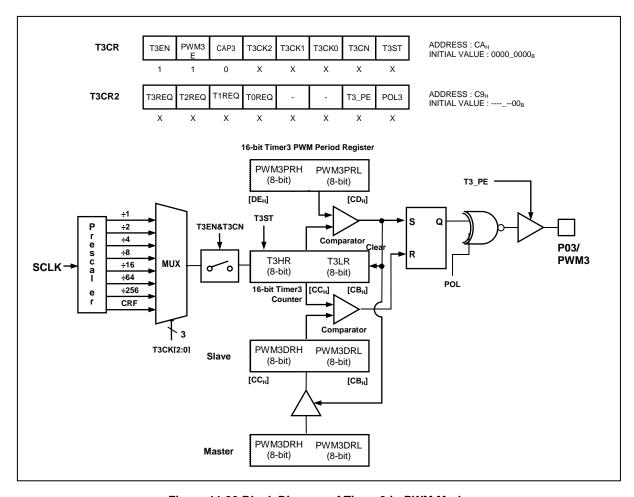

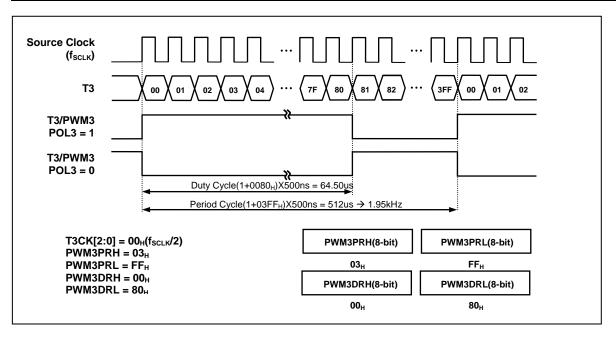

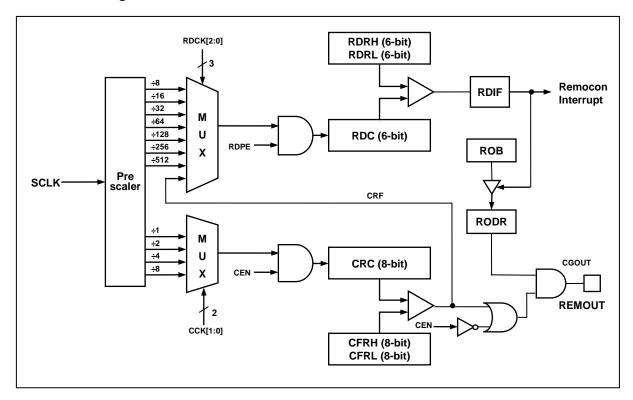

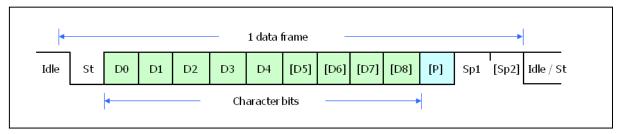

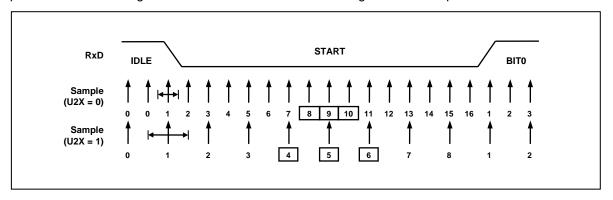

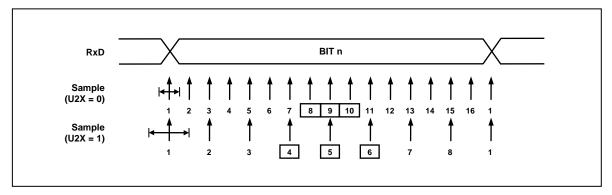

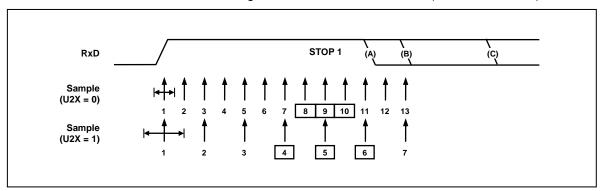

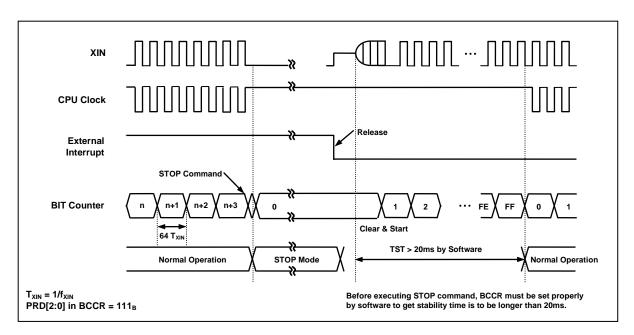

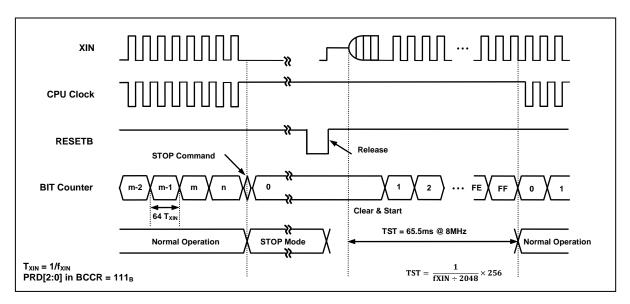

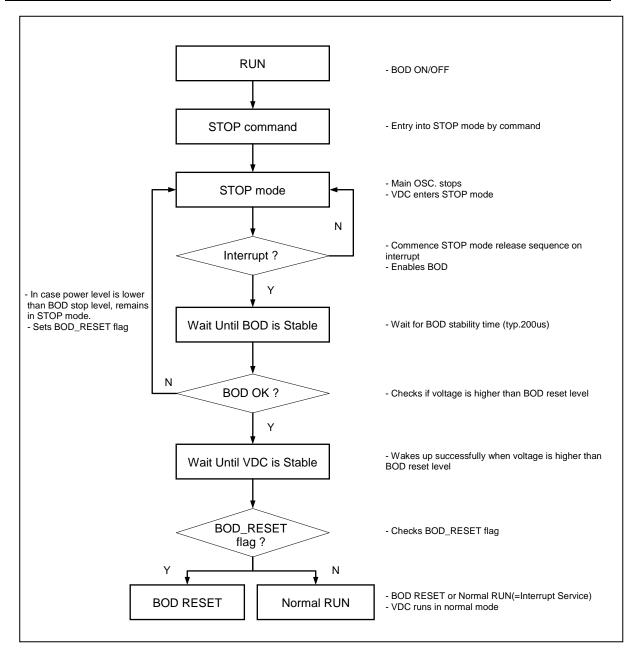

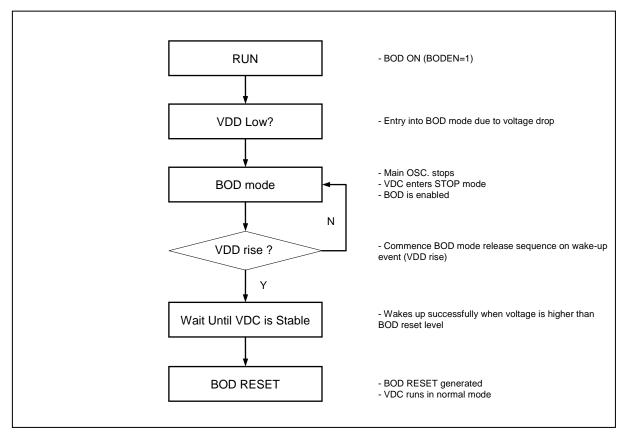

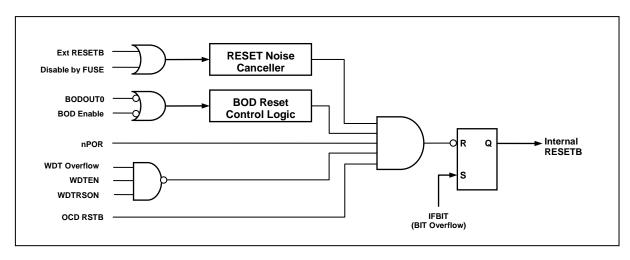

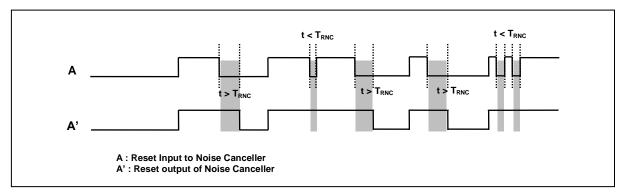

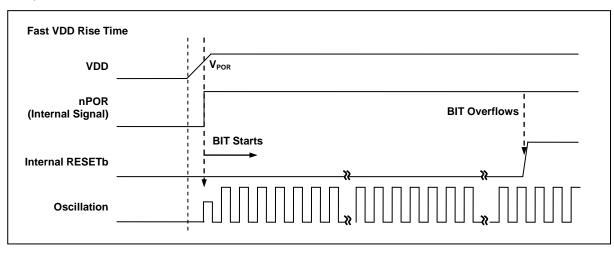

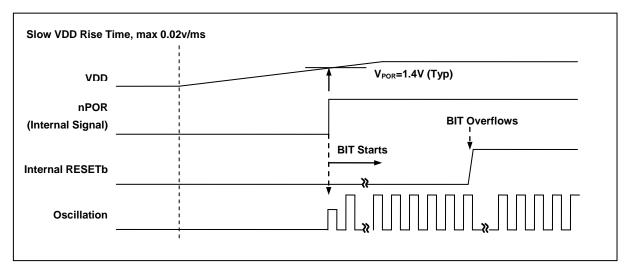

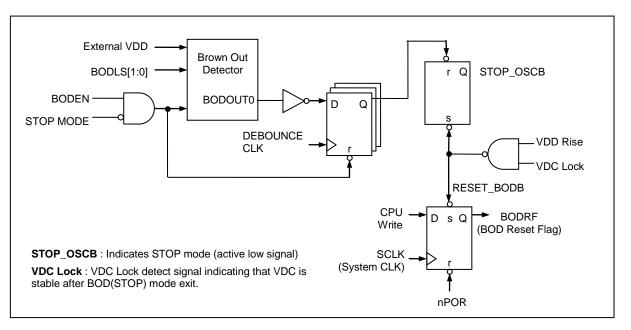

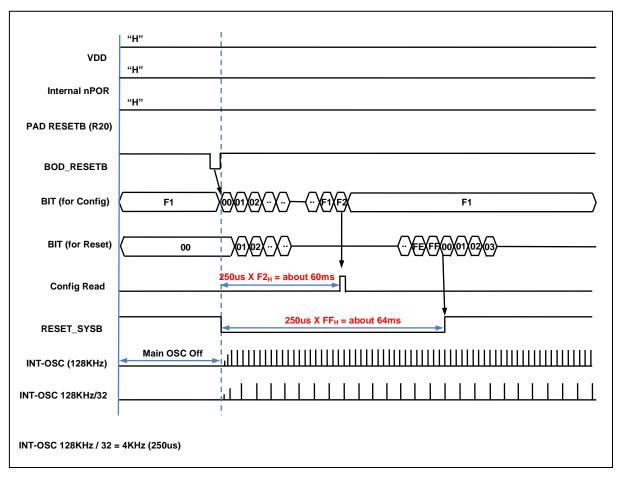

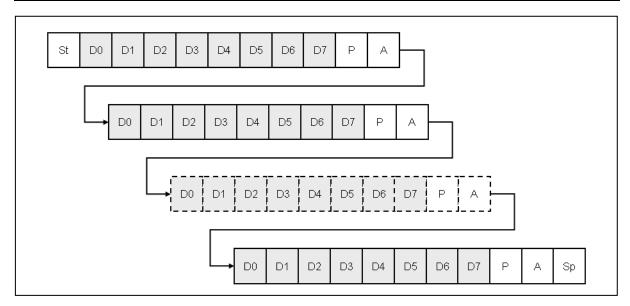

- global enable by EA bit and selective control by IEx bit